本文介绍了设计滤波器的FPGA实现步骤,并结合杜勇老师的书籍中的并行FIR滤波器部分进行一步步实现硬件设计,对书中的架构做了复现以及解读,并进行了仿真验证。

FIR滤波器的结构形式时,介绍了直接型、级联型、频率取样型和快速卷积型4种。在FPGA实现时,最常用的是最简单的直接型结构。FPGA实现直接型结构的FIR滤波器,可以采用串行结构、并行结构等不同中的结构设计,上文根据书中提供的架构完成了串行 FIR滤波器的实现,本文沿用上文的基本代码结构,按照并行FIR滤波器的架构完成电路描述。

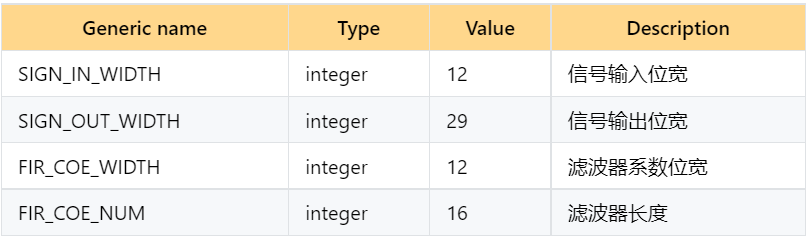

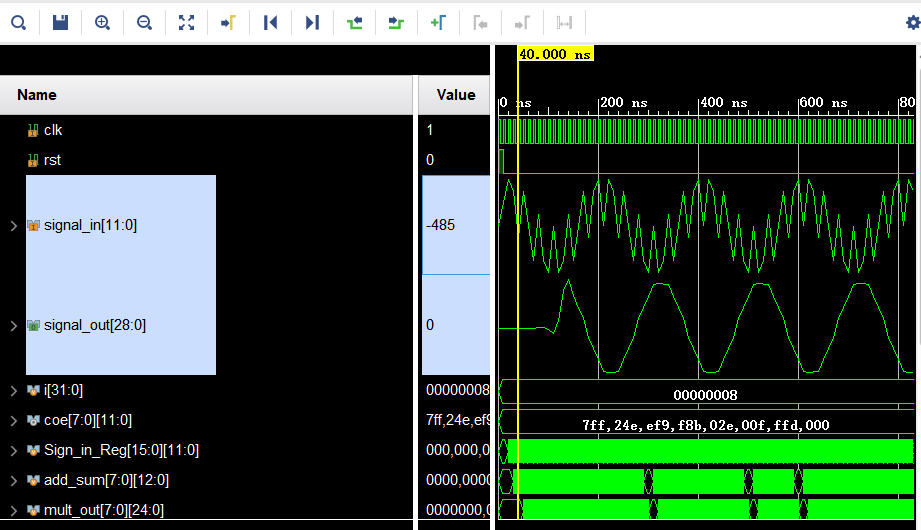

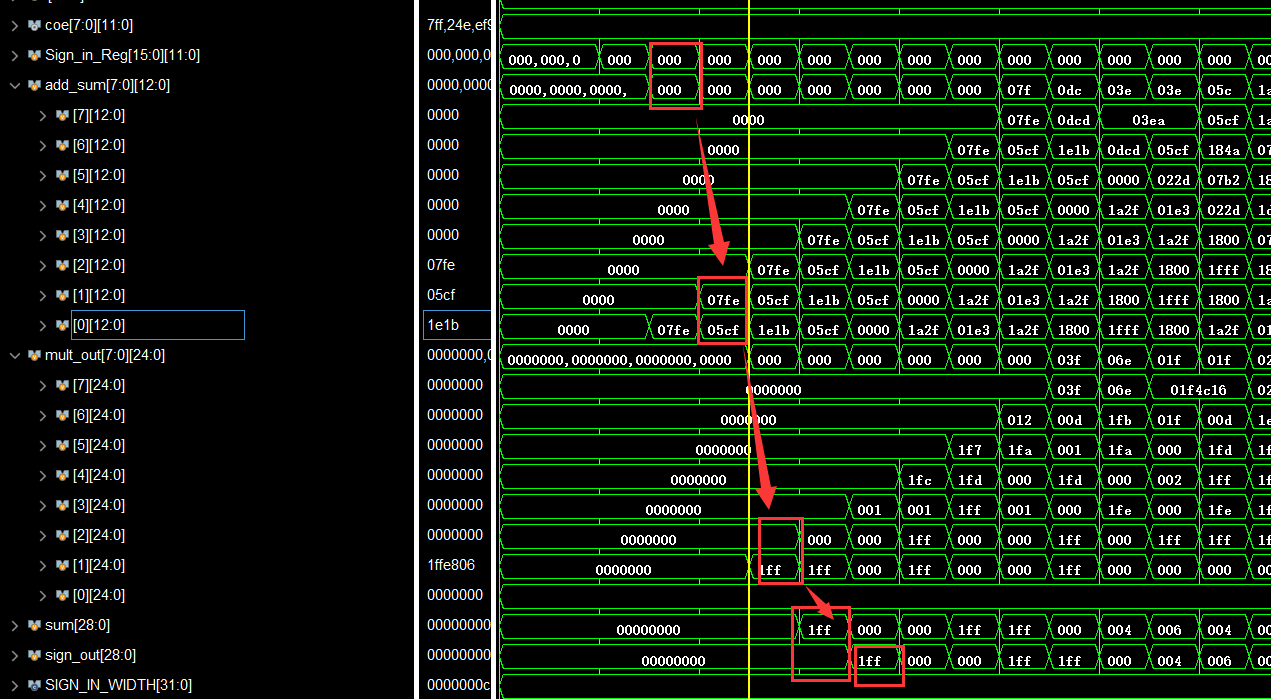

设计一个15阶(长度为16)的低通线性相位FIR滤波器,采用窗函数设计,截止频率为500 Hz,采样频率为2 000 Hz;采用FPGA实现并行结构的滤波器,系数的量化位数为12比特,输入数据位宽为12比特,输出数据位宽为29比特,系统时钟为16 kHz。

确定滤波器的结构后,就根据滤波器进行设计代码仿真,这里引用书中的仿真设计,并将滤波器参数系数量化。确定滤波器系数的方法有很多,可以使用MATLAB中丰富的函数实现,或者使用相关滤波器设计的软件工具,定制满足当前需求的窗函数的滤波器系数。具体量化系数确定可参考上文《数字信号处理-09-串行FIR滤波器MATLAB与FPGA实现》中的相关内容,或者参考杜勇老师的书中的内容。

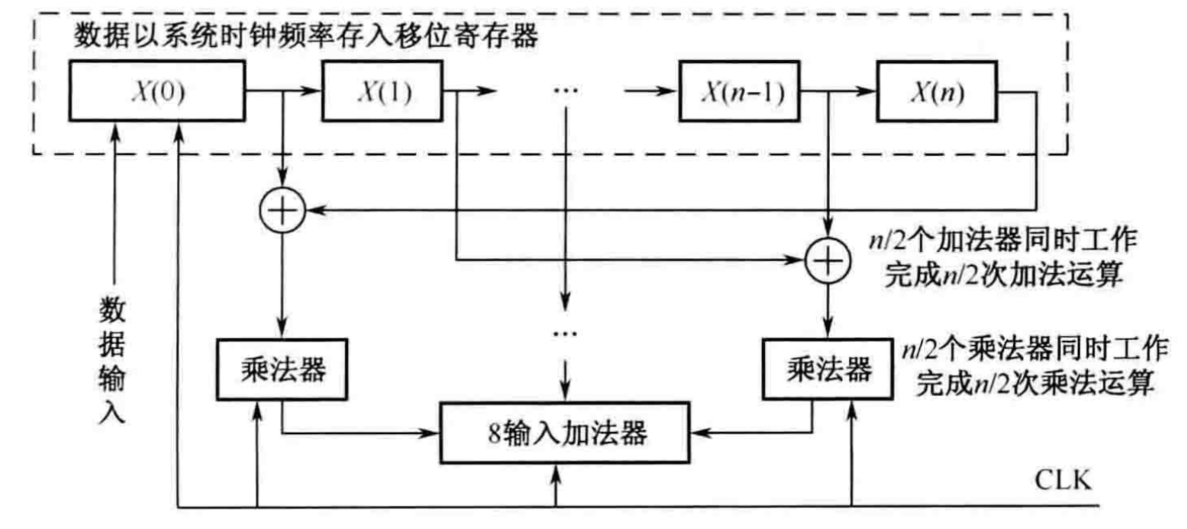

下图为杜勇老师的《数字滤波器的MATLAB与FPGA实现》实现的并行FIR滤波器的结构图。因为FIR滤波器参数对称,所以同时计算相应的对称结构的值,将对称系数的X(n)相加后,可调用8个乘法器,完成对滤波器的乘法运算,所以针对并行滤波器的架构数据的输入速率和时钟可以相同,每一个时钟周期流水输出一个滤波后的信号值。图中的8输入的加法器,可以替换成N/2;这样就得到了一个通用化的并行FIR滤波器结构图。

并行实现FIR滤波器,虽然浪费了加法器和乘法器的资源,但是提升了整个滤波器实现的性能,当滤波器的系数长度N增大时,数据的吞吐速率不变(暂且不考虑面积增大对性能的影响),但带来的坏处就是会用掉相应倍数的逻辑资源和运算资源,速度和面积本来就是鱼和熊掌的关系,在实际应用中应当做相应的权衡和割舍。

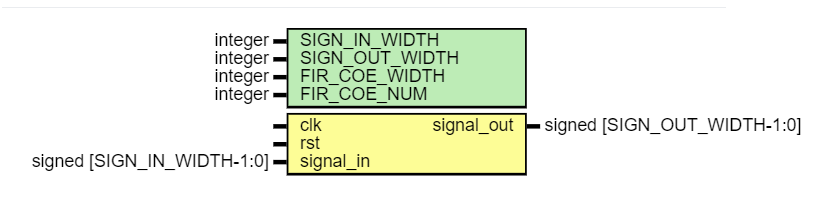

根据杜勇老师书中提供的架构,对电路进行描述,同样沿用了前文的通用化的模板,后期可根据参数输入来适配不同滤波器长度的设计。

接口描述如下:

参数描述如下:

代码如下:

`timescale 1ns / 1ps

module Fir_Parallel(

input clk,//!系统时钟

input rst,//!复位信号

input signed [SIGN_IN_WIDTH-1:0] signal_in,//!信号输入

output signed [SIGN_OUT_WIDTH-1:0] signal_out//!信号输出,信号输出速度和输入速度相同

);

//

parameter integer SIGN_IN_WIDTH = 12 ;//!信号输入位宽

parameter integer SIGN_OUT_WIDTH = 29 ;//!信号输出位宽

parameter integer FIR_COE_WIDTH = 12 ;//!滤波器系数位宽

parameter integer FIR_COE_NUM = 16 ;//!滤波器长度

localparam integer FIR_WIDTH_DIV_2 = FIR_COE_NUM/2 ;

function [FIR_COE_WIDTH-1:0] coe_data;

input [FIR_WIDTH_DIV_2-1:0] index;

begin

case(index)

'd0:coe_data='h000;

'd1:coe_data='hffd;

'd2:coe_data='h00f;

'd3:coe_data='h02e;

'd4:coe_data='hf8b;

'd5:coe_data='hef9;

'd6:coe_data='h24e;

'd7:coe_data='h7ff;

endcase

end

endfunction

integer i;

genvar j;

//!滤波器系数加载

wire signed [FIR_COE_WIDTH-1:0] coe[FIR_WIDTH_DIV_2-1:0];

generate

for (j=0; j<FIR_WIDTH_DIV_2; j=j+1)

assign coe[j] = coe_data(j);

endgenerate

//!寄存输入信号

reg [SIGN_IN_WIDTH-1:0] Sign_in_Reg[FIR_COE_NUM-1:0];

//将数据存入移位寄存器sign_in_Reg中

always @(posedge clk)begin

if (rst=='b1)begin

//初始化寄存器值为0

for (i=0; i<FIR_COE_NUM; i=i+1)

Sign_in_Reg[i]=12'd0;

end

else begin

for (i=0; i<FIR_COE_NUM-1; i=i+1)

Sign_in_Reg[i+1] <= Sign_in_Reg[i];

Sign_in_Reg[0] <= signal_in;

end

end

reg signed [SIGN_IN_WIDTH:0] add_sum[FIR_WIDTH_DIV_2-1:0];

//为了保证加法运算不溢出,输入输出数据均扩展为SIGN_IN_WIDTH+1比特。

//对称结构只需要计算FIR_WIDTH_DIV_2次

//一级流水

always @(posedge clk) begin

if (rst=='b1)begin

for (i=0; i<FIR_WIDTH_DIV_2; i=i+1)

add_sum[i]<= 'd0;

end

else begin

for (i=0; i<FIR_WIDTH_DIV_2; i=i+1)

add_sum[i]<= {Sign_in_Reg[i][SIGN_IN_WIDTH-1],Sign_in_Reg[i]} +

{Sign_in_Reg[FIR_COE_NUM-1-i][SIGN_IN_WIDTH-1],Sign_in_Reg[FIR_COE_NUM-1-i]};

end

end

(*use_dsp48="yes"*) reg signed [SIGN_IN_WIDTH+FIR_COE_WIDTH:0] mult_out[FIR_WIDTH_DIV_2-1:0];

always @(posedge clk ) begin

if (rst=='b1)begin

for (i=0; i<FIR_WIDTH_DIV_2; i=i+1)

mult_out[i]<= 'd0;

end

else begin

for (i=0; i<FIR_WIDTH_DIV_2; i=i+1)

mult_out[i] <= add_sum[i] * coe[i];

end

end

assign signal_out = sign_out;

reg signed [SIGN_OUT_WIDTH-1:0] sum;

reg signed [SIGN_OUT_WIDTH-1:0] sign_out;

always @(posedge clk)begin

if (rst)begin

sum <= 'd0;

sign_out <= 'd0;

end

else begin

sign_out <= sum;

// sum = 'd0;

// for (i=0; i<FIR_WIDTH_DIV_2; i=i+1)

// sum = sum + mult_out[i];

sum <= mult_out[0] + mult_out[1] + mult_out[2] + mult_out[3] +

mult_out[4] + mult_out[5] + mult_out[6] + mult_out[7];

end

end

endmodule

关于加载滤波器系数的部分,我这里使用了function做了包装,以便于后续修改滤波器长度时,可以通过脚本生成function去增加滤波器系数的长度。

function [FIR_COE_WIDTH-1:0] coe_data;

input [FIR_WIDTH_DIV_2-1:0] index;

begin

case(index)

'd0:coe_data='h000;

'd1:coe_data='hffd;

'd2:coe_data='h00f;

'd3:coe_data='h02e;

'd4:coe_data='hf8b;

'd5:coe_data='hef9;

'd6:coe_data='h24e;

'd7:coe_data='h7ff;

endcase

end

endfunction

针对乘法运算,这里没有使用IP,但是为了使得该部分运算使用DSP资源,更好地提升性能,因此该信号的运算使用dsp48资源,所以在信号声明时前面加了(*use_dsp48="yes"*)。

关于杜勇老师书中写的信号与系数相乘后的结果针对sum信号使用了阻塞赋值的部分,个人觉得这个在时序逻辑中是不太好的设计,使用的代码如下,虽然会简化乘累加的过程,但是针对实际使用的工程来说,这个是不好的代码风格。

always @(posedge clk)begin

if (rst=='b1)begin

sum = 'd0;

sign_out <= 'd0;

end

else begin

sign_out <= sum;

sum = 'd0;

for (i=0; i<FIR_WIDTH_DIV_2; i=i+1)

sum = sum + mult_out[i];

end

end

所以这里我直接做了展开处理,将8个结果做了加法。

我认为在随着滤波器规模变大运算的数据位宽增加时,信号与系数相乘后的结果进行累加操作的部分,组合逻辑的延时相对会增加很多,为了进一步提升电路架构的性能,可对该部分进行加法树的平衡,打拍优化加法树结构,应该有可能进一步提升电路架构的性能。

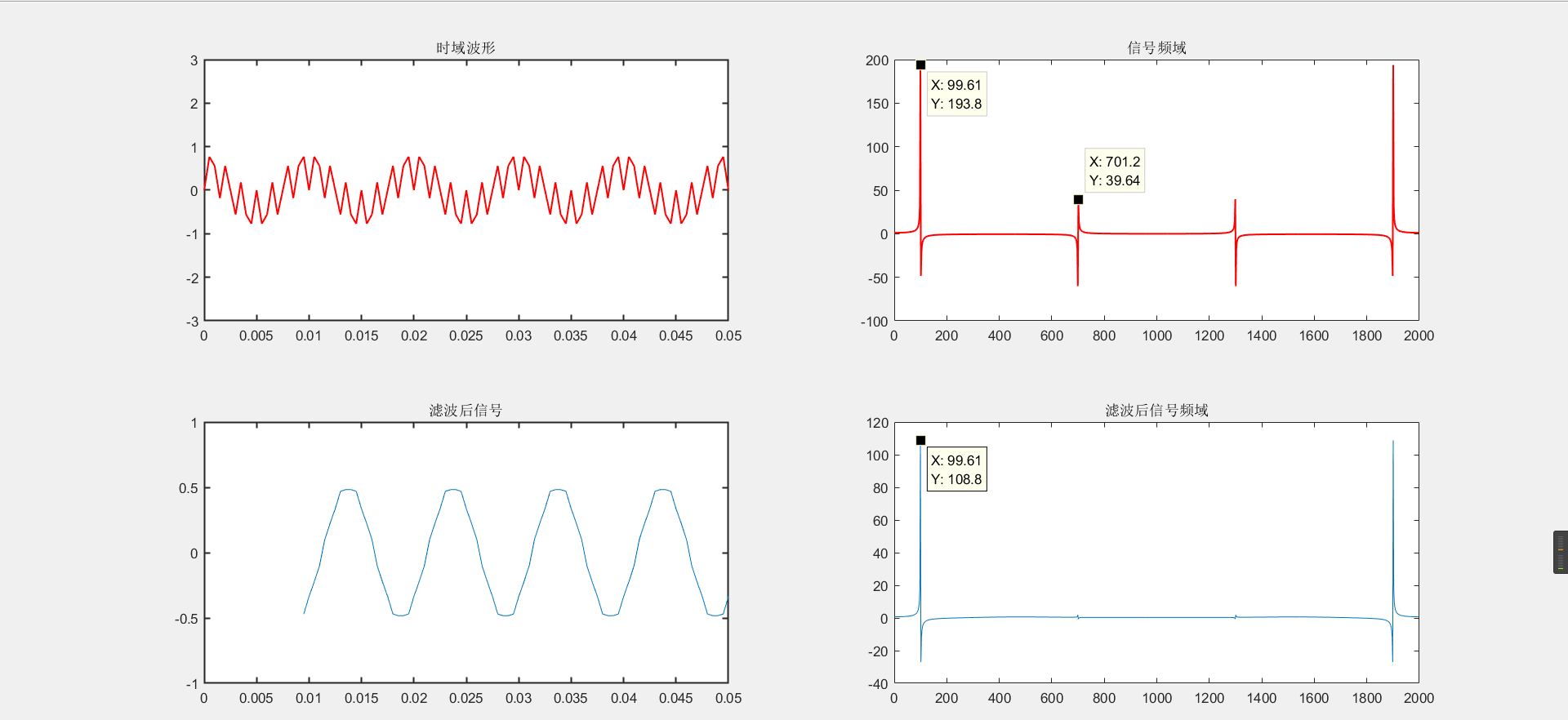

为了验证并行设计代码的正确性。这里使用MATLAB脚本产生了一个混频信号,混频的频率为100hz和700hz的叠加,然后将混频信号进行量化处理并导出txt文件以供仿真文件读取。

clc;close all;clear all;

Fs = 2000; %采样频率

N = 2^10; %采样点数

f1=300; %正弦波1频率

f2=400; %正弦波1频率

t=[0:N-1]/Fs; %时间序列

s1 = sin(2*pi*f1*t) ;

s2 = sin(2*pi*f2*t) ;

s = s1 .* s2;

figure(1);

subplot(1,2,1);

plot(t,s,'r','LineWidth',1.2);

title('时域波形');

axis([0,100/Fs,-3,3]);

set(gca,'LineWidth',1.2);

%转化为位宽12bit数据

s_12bit=s./max(s).*(2.^11 - 1); % DA输入波形,量化到16bit

s_12bit(find(s_12bit<0) ) = s_12bit(find(s_12bit<0) ) + 2^12 - 1;

s_12bit = fix(s_12bit);

s_12bit = dec2hex(s_12bit);

% %生成文件

fid= fopen('sin_data.txt','w+');

%生成十六进制

for i=1:N

fprintf(fid,'%s',s_12bit(i,:));

fprintf(fid,'\r\n');

end

fclose(fid);

%% 设计验证

N=16; %滤波器长度

fs=2000; %采样频率

fc=500; %低通滤波器的截止频率

B=12; %量化位数

%生成各种窗函数

w_kais=blackman(N)';

%采用fir1函数设计FIR滤波器

b_kais=fir1(N-1,fc*2/fs,w_kais);

ss=conv(b_kais,s);

subplot(1,2,2);

plot(t(20:1000),ss(20:1000));

title('滤波后信号');

axis([0,100/Fs,-1,1]);

set(gca,'LineWidth',1.2);

运行仿真后,根据设计的滤波器系数进行仿真,发现可以正常滤波除去高频分量。

`timescale 1ns / 1ps

module Fir_Parallel_tb;

// Parameters

localparam integer SIGN_IN_WIDTH = 12;

localparam integer SIGN_OUT_WIDTH = 29;

localparam integer FIR_COE_WIDTH = 12;

localparam integer FIR_COE_NUM = 16;

// Ports

reg clk = 1;

reg rst = 1;

reg [SIGN_IN_WIDTH-1:0] signal_in;

wire [SIGN_OUT_WIDTH-1:0] signal_out;

Fir_Parallel #(

.SIGN_IN_WIDTH(SIGN_IN_WIDTH ),

.SIGN_OUT_WIDTH(SIGN_OUT_WIDTH ),

.FIR_COE_WIDTH(FIR_COE_WIDTH ),

.FIR_COE_NUM (FIR_COE_NUM )

)Fir_Parallel_dut (

.clk (clk ),

.rst (rst ),

.signal_in (signal_in ),

.signal_out ( signal_out)

);

reg [11:0] mem [0:99];

reg [9:0] addr ;

// reg [11:0]data_out ;

always #(10*1)

begin

if(rst==0)

addr = addr + 10'd1;

signal_in = mem[addr][11:0];

end

always

#5 clk = ! clk ;

initial

begin

signal_in =0;

$readmemh("sin_data.txt",mem);

addr = 10'd0;

#10;

rst = 0;

end

endmodule

运行仿真,查看波形可见,滤波效果和仿真结果一致。

该架构的数据输入后,每四个时钟周期后输出一个数据,其中,一个时钟周期用于X(n)的加和,一个时钟周期用于计算信号和滤波器系数相乘的结果,一个时钟周期用于乘法输出后的数据做累加处理,一个时钟用于读取累加后的结果。

Rackup通过Rack的默认处理程序成功运行任何Rack应用程序。例如:classRackAppdefcall(environment)['200',{'Content-Type'=>'text/html'},["Helloworld"]]endendrunRackApp.new但是当最后一行更改为使用Rack的内置CGI处理程序时,rackup给出“NoMethodErrorat/undefinedmethod`call'fornil:NilClass”:Rack::Handler::CGI.runRackApp.newRack的其他内置处理程序也提出了同样的反对意见。例如Rack

我正在尝试解析一个CSV文件并使用SQL命令自动为其创建一个表。CSV中的第一行给出了列标题。但我需要推断每个列的类型。Ruby中是否有任何函数可以找到每个字段中内容的类型。例如,CSV行:"12012","Test","1233.22","12:21:22","10/10/2009"应该产生像这样的类型['integer','string','float','time','date']谢谢! 最佳答案 require'time'defto_something(str)if(num=Integer(str)rescueFloat(s

matlab打开matlab,用最简单的imread方法读取一个图像clcclearimg_h=imread('hua.jpg');返回一个数组(矩阵),往往是a*b*cunit8类型解释一下这个三维数组的意思,行数、数和层数,unit8:指数据类型,无符号八位整形,可理解为0~2^8的数三个层数分别代表RGB三个通道图像rgb最常用的是24-位实现方法,即RGB每个通道有256色阶(2^8)。基于这样的24-位RGB模型的色彩空间可以表现256×256×256≈1670万色当imshow传入了一个二维数组,它将以灰度方式绘制;可以把图像拆分为rgb三层,可以以灰度的方式观察它figure(1

目录一.加解密算法数字签名对称加密DES(DataEncryptionStandard)3DES(TripleDES)AES(AdvancedEncryptionStandard)RSA加密法DSA(DigitalSignatureAlgorithm)ECC(EllipticCurvesCryptography)非对称加密签名与加密过程非对称加密的应用对称加密与非对称加密的结合二.数字证书图解一.加解密算法加密简单而言就是通过一种算法将明文信息转换成密文信息,信息的的接收方能够通过密钥对密文信息进行解密获得明文信息的过程。根据加解密的密钥是否相同,算法可以分为对称加密、非对称加密、对称加密和非

目录前言滤波电路科普主要分类实际情况单位的概念常用评价参数函数型滤波器简单分析滤波电路构成低通滤波器RC低通滤波器RL低通滤波器高通滤波器RC高通滤波器RL高通滤波器部分摘自《LC滤波器设计与制作》,侵权删。前言最近需要学习放大电路和滤波电路,但是由于只在之前做音乐频谱分析仪的时候简单了解过一点点运放,所以也是相当从零开始学习了。滤波电路科普主要分类滤波器:主要是从不同频率的成分中提取出特定频率的信号。有源滤波器:由RC元件与运算放大器组成的滤波器。可滤除某一次或多次谐波,最普通易于采用的无源滤波器结构是将电感与电容串联,可对主要次谐波(3、5、7)构成低阻抗旁路。无源滤波器:无源滤波器,又称

MIMO技术的优缺点优点通过下面三个增益来总体概括:阵列增益。阵列增益是指由于接收机通过对接收信号的相干合并而活得的平均SNR的提高。在发射机不知道信道信息的情况下,MIMO系统可以获得的阵列增益与接收天线数成正比复用增益。在采用空间复用方案的MIMO系统中,可以获得复用增益,即信道容量成倍增加。信道容量的增加与min(Nt,Nr)成正比分集增益。在采用空间分集方案的MIMO系统中,可以获得分集增益,即可靠性性能的改善。分集增益用独立衰落支路数来描述,即分集指数。在使用了空时编码的MIMO系统中,由于接收天线或发射天线之间的间距较远,可认为它们各自的大尺度衰落是相互独立的,因此分布式MIMO

我明白了:x,(y,z)=1,*[2,3]x#=>1y#=>2z#=>nil我想知道为什么z的值为nil。 最佳答案 x,(y,z)=1,*[2,3]右侧的splat*是内联扩展的,所以它等同于:x,(y,z)=1,2,3左边带括号的列表被视为嵌套赋值,所以它等价于:x=1y,z=23被丢弃,而z被分配给nil。 关于ruby-带括号和splat运算符的并行赋值,我们在StackOverflow上找到一个类似的问题: https://stackoverflow

假设您在Ruby中执行此操作:ar=[1,2]x,y=ar然后,x==1和y==2。是否有一种方法可以在我自己的类中定义,从而产生相同的效果?例如rb=AllYourCode.newx,y=rb到目前为止,对于这样的赋值,我所能做的就是使x==rb和y=nil。Python有这样一个特性:>>>classFoo:...def__iter__(self):...returniter([1,2])...>>>x,y=Foo()>>>x1>>>y2 最佳答案 是的。定义#to_ary。这将使您的对象被视为要分配的数组。irb>o=Obje

在Ruby中,是否有一种简单的方法可以将n维数组中的每个元素乘以一个数字?这样:[1,2,3,4,5].multiplied_by2==[2,4,6,8,10]和[[1,2,3],[1,2,3]].multiplied_by2==[[2,4,6],[2,4,6]]?(很明显,我编写了multiplied_by函数以区别于*,它似乎连接了数组的多个副本,不幸的是这不是我需要的)。谢谢! 最佳答案 它的长格式等价物是:[1,2,3,4,5].collect{|n|n*2}其实并没有那么复杂。你总是可以使你的multiply_by方法:c

我对图像处理完全陌生。我对JPEG内部是什么以及它是如何工作一无所知。我想知道,是否可以在某处找到执行以下简单操作的ruby代码:打开jpeg文件。遍历每个像素并将其颜色设置为fx绿色。将结果写入另一个文件。我对如何使用ruby-vips库实现这一点特别感兴趣https://github.com/ender672/ruby-vips我的目标-学习如何使用ruby-vips执行基本的图像处理操作(Gamma校正、亮度、色调……)任何指向比“helloworld”更复杂的工作示例的链接——比如ruby-vips的github页面上的链接,我们将不胜感激!如果有ruby-