文章目录

学习不能稀里糊涂,要学会多思考,发散式学习以及总结:

FPGA作为一种器件,只是实现目的的一种方法,过度追求实现的技术细节(用hdl还是hls,用啥芯片,用啥接口)容易只见树木不见森林。工具软件的用法也好,器件的架构也好,语言孰优孰劣的争论也罢。工程应用里大概更多应该去考虑适合的实现方式,现在software define network/flash/xxx,已然大势所趋,算法是纲,纲举目张。是因为在实现上需要有流水线,多路并行,快速部署的目的所以考虑使用FPGA,而不是为了使用而使用。

不管实现目的的方法是FPGA还是DSP甚至是GPU,这些都是工具,工程师的核心竞争力除了在于熟练地掌握开发的技巧。更重要的在于信号与系统、数字信号处理、图像处理之类的让你了解算法、优化算法的基石;以及数字电路、微机原理、处理器体系结构这些让你了解为什么这些工具要这样设计,要这样发展的课程(系统学习一点体系结构,那么这些数据级并行、指令级并行、线程级并行的处理器就不再陌生了)工程师应该顶天(了解应用,了解算法)也应该立地(了解工具,掌握技巧)。

——引用某个大佬的话,作为学习共勉

简单来说就是:FPGA是工具用来搬砖,更多的知识在FPGA之外

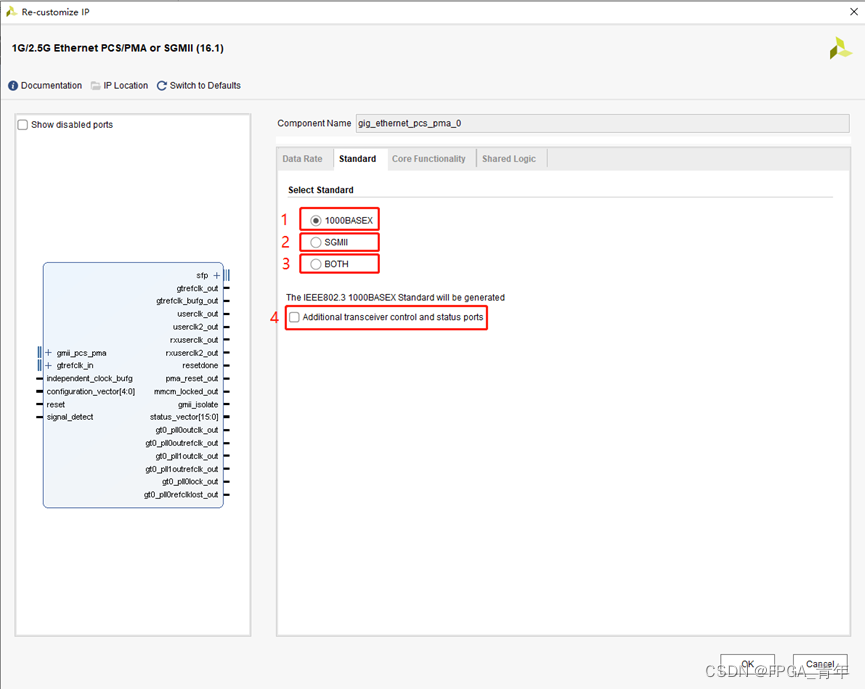

选择Ethernet下的“1G/2.5G Ethernet PCS/PMA or SGMII”IP核

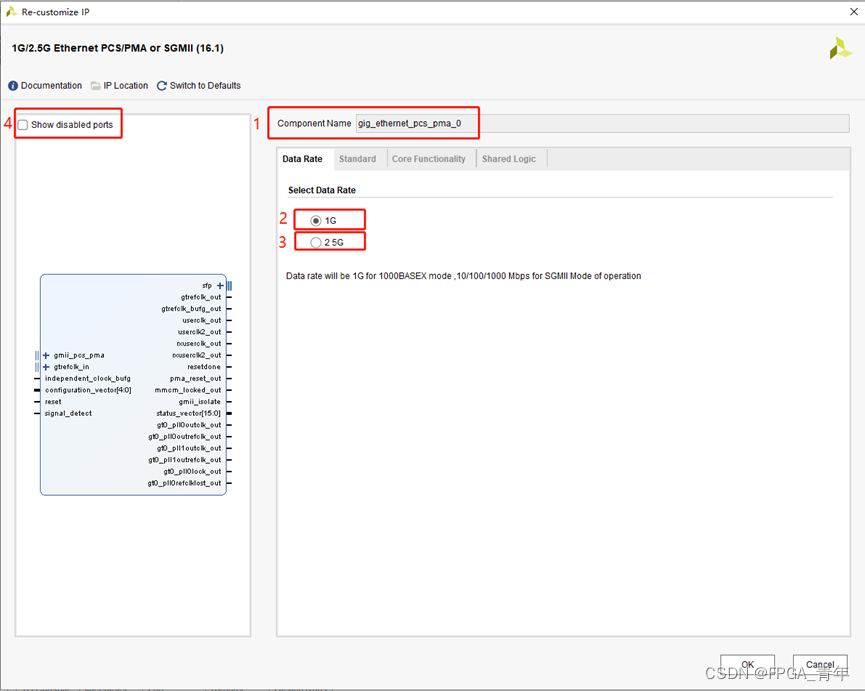

IP核配置

1:IP核的名字;

4:点击是否展开所有引脚(没必要点击);

2、3:IP核提供了两种数据速率1GMbps和2.5Gmbps,选择1G;

该IP提供了用于生成1000BASE-X,2500BASE-X,1G SGMII和2.5G SGMII四种标准应用。关于选择BASEX还是SGMII我们需要根据我们实际应用的接口选择;在这里我们参考该IP核文档pg047中的介绍:

查找文档以及使用方法可以参考这篇文章:

vivado的DocNav学习;FPGA芯片外挂DDR个数_FPGA_青年的博客-CSDN博客

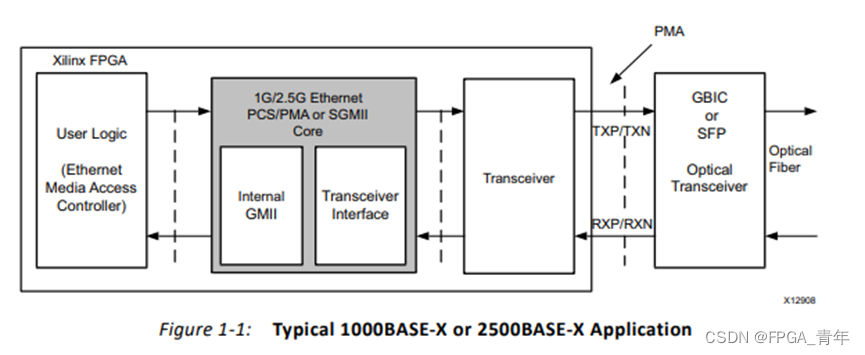

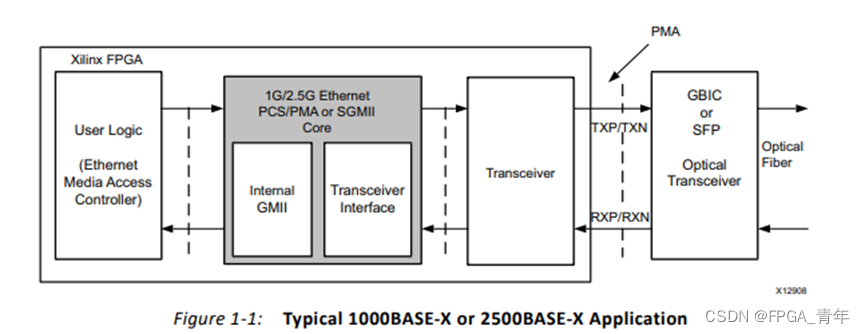

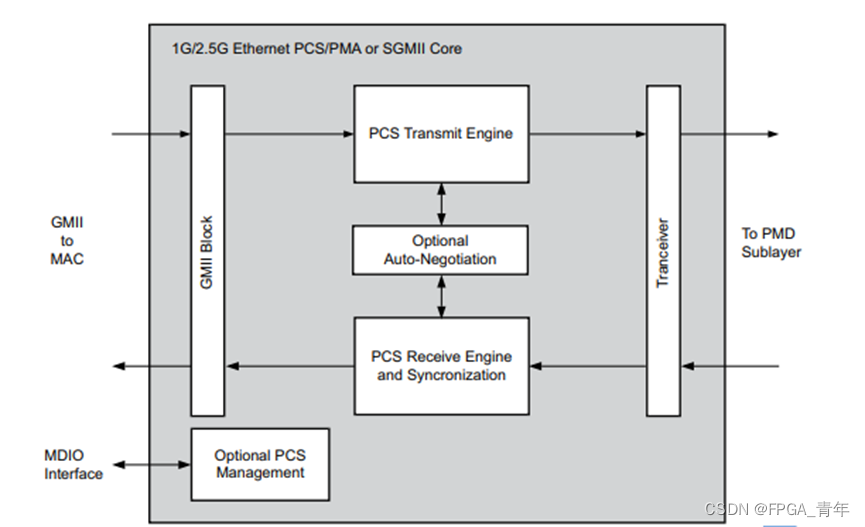

1)、(figure1-1)设备专用GT收发器支持PMA连接到外部现成的千兆接口转换器 (GBIC) 或小型可插拔 (SFP) 光收发器,以完成以太网端口,BASEX只能连接这两种器件(本次设计使用GBIC )。这里可以理解为MAC层+PCS层+PMA层以串型的方式与PHY层的PMD相连,TX/RX分别为从PMA到PMD的串行传输的差分输出,从PMD到PMA的串行传输的差分输入。

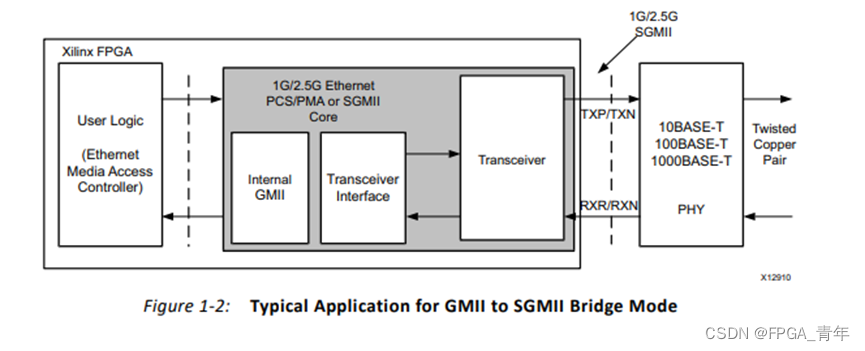

2)、(figure1-2)设备专用GT收发器也支持1g或2.5G SGMII连接到外部现成以太网PHY设备(RJ-45电口)。它也能为1G提供三模式PHY芯片的10BASE-T, 100BASE-T, and 1000BASE-T。

SGMII本质上并没有对以太网协议的分层做改动,还是MAC层,PCS层和PMA层。原来GMII模式下,MAC层一般做在FPGA侧,PHY层包括PCS+PMA做在另一个单独的芯片上。而SGMII的实施是将PCS层也同时放在了原来的MAC侧。这样FPGA芯片和PHY芯片各有一个PCS层。

对于FPGA发送来说,数据包有MAC层过来,经过TX的PCS,从SGMII接口发送出去。在PHY芯片上,有一个RX的PCS先将SGMII的信号解出GMII信号,然后再经过传统的PHY层处理发送到介质上。对于FPGA接收来说,则反过来。

关于PHY层的知识,大家可以参考此文章。

以太网学习之MAC与PHY间通信_FPGA_青年的博客-CSDN博客

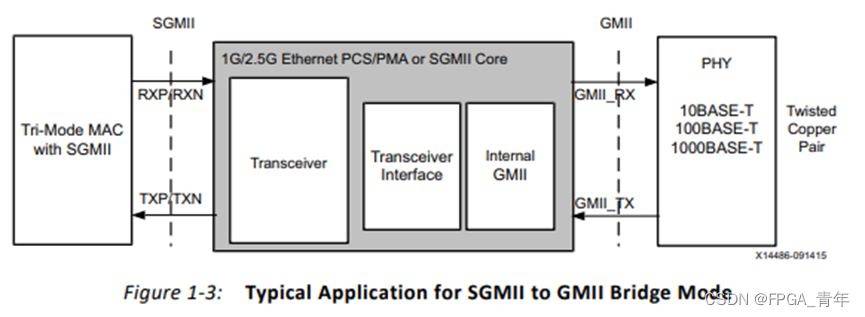

3)、(figure1-3)它也可以作为三速以太网(Tri Mode Ethernet MAC)IP核SGMII转换成GMII的桥梁。

1:1000BASEX:将生成IEE802.3 1000BASEX的标准,是千兆以太网光口的物理接口命名,属于物理层接口,可以称为物理相关接口,1000BASEX只支持1000速率,后缀BASE不持支自协商;采用光口(SFP)作为网络接口时使用( 本次设计我们选择1000BASEX );

2:SGMII:将生成GMII到Serial-GMII(SGMII)桥;可以称为媒体独立接口,SGMII支持10/100/1000速率,可以根据实际进行自协商速率转换,采用电口(RJ45)或是需要转换成GMII等信号时使用;

3:BOTH:在1000BASE-X和SGMIL标准之间进行动态切换,哪个稳定先与哪个建立连接;

4:附加收发器控制和状态端口;(暂时没有用到附加端口,不选择)

补充:

在编写代码的时候,是在用户端即上图中的User Logic处编写代码,中间为IP核内部逻辑不用管,右侧为外接接口,需要上板测试的时候需要分配此引脚(RX、TX等)。

1000表示千兆速率,base表示基带传输,X表示采用了8B/10B分组码编码方式,详细介绍可以看上一篇文章的第三部分内容:

FPGA平台以太网学习:涉及1G/2.5G Ethernet 和Tri Mode Ethernet MAC两个IP核的学习记录(一)——知识补给_FPGA_青年的博客-CSDN博客。

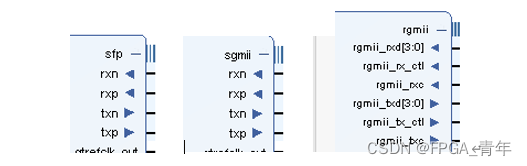

在下图中,左图是选择1000BASEX产生的外接接口SFP,中间图为选择SGMII产生的外接接口sgmii,最右边的是三速以太网IP(Tri Mode Ethernet MAC)的RGMII接口(还可以更换成GMII/MII/Internal),后边将会讲解三速以太网,到时候可以对比学习;

我们可以看到1G/2.5G Ethernet PCS/PMA or SGMII 以太网IP核采用的是RXN,RXP,TXN,TXP差分串行数据接口,此IP核采用的是FPGA芯片的GT(Gigabit Transceiver )高速收发器作为千兆网通信对外的接口。(关于GT高速收发器的知识后续有时间整理)大家可以在此大佬的文章进行学习:

Xilinx FPGA平台GTX简易使用教程(汇总篇)_fpga gtx_子墨祭的博客-CSDN博客

采用1G/2.5G Ethernet PCS/PMA or SGMII 以太网IP核时:

1、 FPGA相当于MAC层+PCS层+PMA层(属于PHY层中的一部分,选择1000BASEX);

2、 FPGA相当于MAC层+PCS层(属于PHY层的一部分,选择SGMII)。

在这里我补充一下:我们的数据在数据链路层(MAC)进行数据组帧以后,都需要经过编码PCS层和串并转换PMA层,SGMII接口属于串型接口,因此它只需要经过PCS层。

关于PHY芯片内部协议以及GT收发器的PCS和PMA可以参考这个文章:

FPGA平台以太网学习:MAC与PHY间通信_FPGA_青年的博客-CSDN博客

采用Tri Mode Ethernet MAC以太网IP核时:

1、 FPGA只是MAC层。

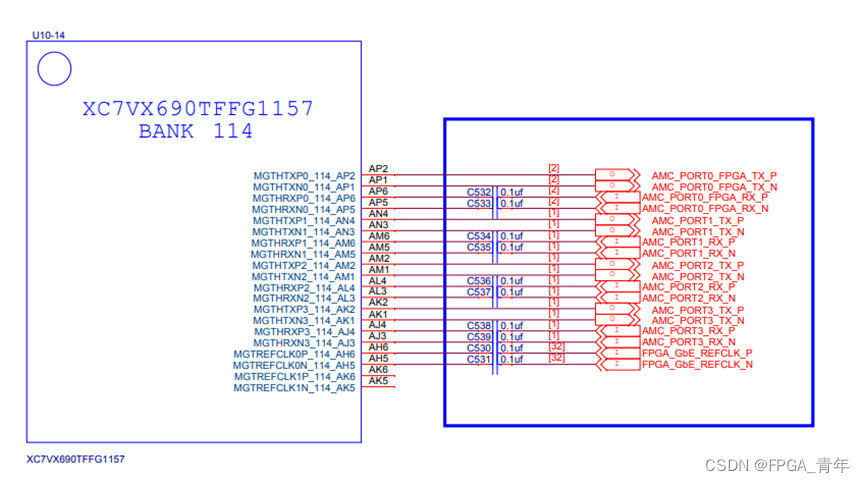

可以看下采用1G/2.5G Ethernet PCS/PMA or SGMII 以太网IP核实际用到的原理图接口,下图中共有4对高速接口port0-port3:

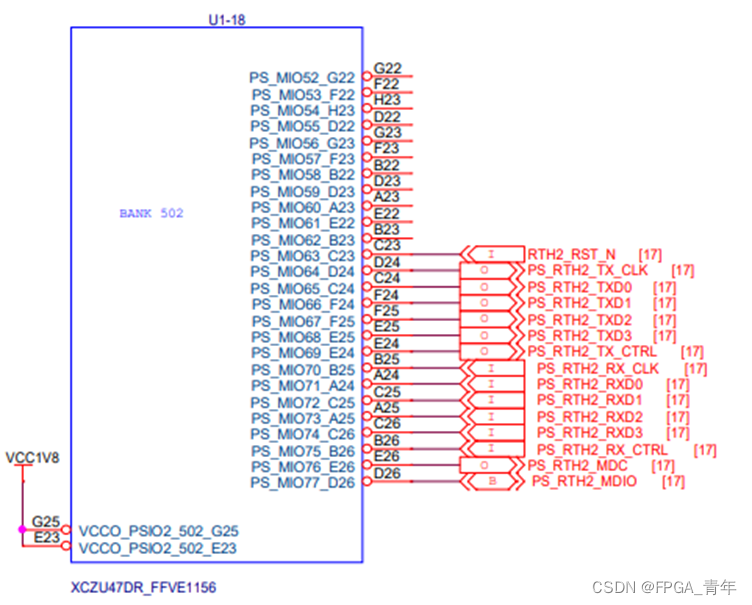

可以看下采用zynq系列时ps端进行千兆网通信的原理引脚图,Tri Mode Ethernet MAC IP核使用到的引脚同样如此。采用RGMII接口。

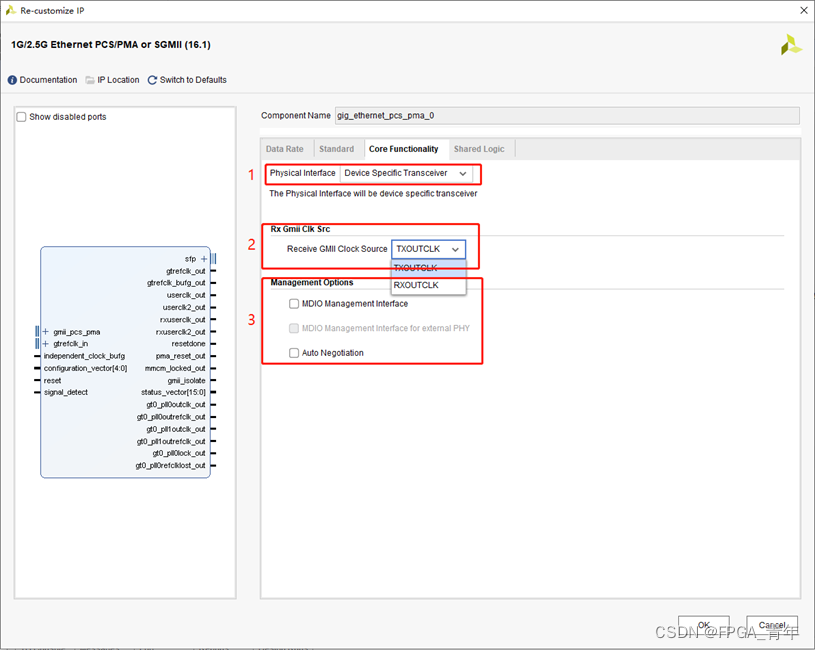

1: 物理接口:设备专用收发器;物理接口将是设备特定的收发器即GT高速收发器,即上边原理图的RT与TX(此处只有一个选项默认);

2:接收GMII时钟源:输入IP核内部的MMCM的时钟源选择为GT收发器输出的时钟TXOUTCLK(默认选项即可),该MMCM将产生我们所需要的接口时钟;

3:管理选项:MDIO管理接口和自协商,这里提一下,采用SGMII外接PHY芯片时候,MDIO是为了配置PHY芯片用的,一般PHY默认配置就可以正常使用(暂时都用不到,不选);可以参考下官方的回答

以太网IP核1G/2.5G Ethernet PCS/PMA or SGMII的问题咨询 (xilinx.com)

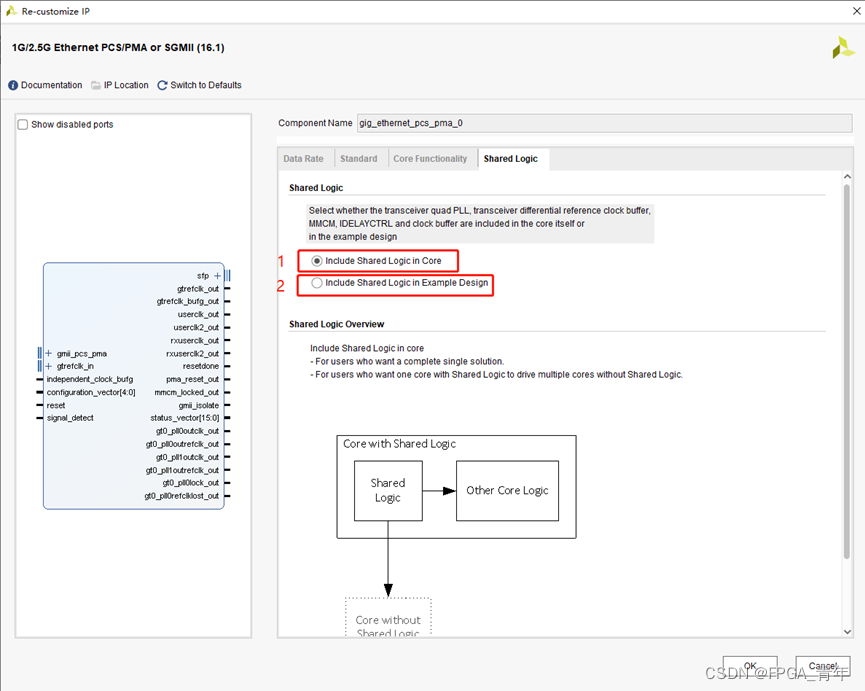

1:核内共享逻辑:设计只采用一个该IP核的时候,就选择此项

2:示例设计中包含共享逻辑:当设计中需要同时使用若干个此IP核,且所使用的GTX均位于同一个GTX BANK中,只需其中1个IP核内部的共享资源(MMCM、GTX PLL、GTX 参考时钟等)便可以满足所有IP核的需求,即选择将共享资源包含在IP核内部。通过共享逻辑可以较小硬件资源的消耗,并且各个接口输出时序是一致的。(暂时没有用到,不选)

在此IP核的配置就结束了,后边将讨论以太网应用中的设计方案

再次强调下,FPGA是工具,要学会使用工具就要看配套资料,IP配置以及接口使用在文档中讲解的都很清楚,不过都是英文的,以下链接简单介绍如何查找文档

vivado的DocNav学习;FPGA芯片外挂DDR个数_FPGA_青年的博客-CSDN博客

关于网口选择部分,我写的挺多的,主要这里边涵盖的知识非常多。主要是想说的时,在做千兆网的时候,FPGA通常采用两种外界接口。

1、一种就是普通接口MII/RMII/GMII/RGMII这些接口,RGMII是最常用的接口,这些接口都属于低速接口。例如上边介绍的ZYNQ的PS端以太网和三速以太网Tri Mode Ethernet MAC IP核这两种都是使用RGMII,与外部PHY芯片进行连接,然后再通过网口。即:FPGA=MAC<–>PHY<–>RG45。

2、还有一种就是采用高速收发器即GT接口作为外接接口,外部接的是TXP/TXN和RXP/RXN这种串型接口,上边普通的采用的是并行接口。GT用于千兆以太网物理编码子层/物理介质连接子层 (Physical Coding Sublayer/Physical Media Dependent PCS/PMA)。

例如本次使用的1G/2.5G Ethernet PCS/PMA or SGMII IP核。这个IP是将PHY芯片的的PMA层和PCS层集合到了FPGA中。即FPGA=MAC+ PCS / PMA。

(1)当采用1000BASEX时候,IP核作为PCS层(编码)+PMA层(并转串),通过收发器向PMD发送,此时FPGA与外部千兆接口转换器 (GBIC) 或小型可插拔 (SFP) 光收发器进行连接。如下图所示:

(2)当采用SGMII时候,IP核作为PCS层,通过收发器向PHY芯片的PCS层发送,此时FPGA与现成以太网PHY设备(RJ-45电口)进行连接。如下图所示:

下一节,将会做接口与框架介绍。

记录美好学习,从总结开始;💪

我有一个存储主机名的Ruby数组server_names。如果我打印出来,它看起来像这样:["hostname.abc.com","hostname2.abc.com","hostname3.abc.com"]相当标准。我想要做的是获取这些服务器的IP(可能将它们存储在另一个变量中)。看起来IPSocket类可以做到这一点,但我不确定如何使用IPSocket类遍历它。如果它只是尝试像这样打印出IP:server_names.eachdo|name|IPSocket::getaddress(name)pnameend它提示我没有提供服务器名称。这是语法问题还是我没有正确使用类?输出:ge

目录前言滤波电路科普主要分类实际情况单位的概念常用评价参数函数型滤波器简单分析滤波电路构成低通滤波器RC低通滤波器RL低通滤波器高通滤波器RC高通滤波器RL高通滤波器部分摘自《LC滤波器设计与制作》,侵权删。前言最近需要学习放大电路和滤波电路,但是由于只在之前做音乐频谱分析仪的时候简单了解过一点点运放,所以也是相当从零开始学习了。滤波电路科普主要分类滤波器:主要是从不同频率的成分中提取出特定频率的信号。有源滤波器:由RC元件与运算放大器组成的滤波器。可滤除某一次或多次谐波,最普通易于采用的无源滤波器结构是将电感与电容串联,可对主要次谐波(3、5、7)构成低阻抗旁路。无源滤波器:无源滤波器,又称

最近在学习CAN,记录一下,也供大家参考交流。推荐几个我觉得很好的CAN学习,本文也是在看了他们的好文之后做的笔记首先是瑞萨的CAN入门,真的通透;秀!靠这篇我竟然2天理解了CAN协议!实战STM32F4CAN!原文链接:https://blog.csdn.net/XiaoXiaoPengBo/article/details/116206252CAN详解(小白教程)原文链接:https://blog.csdn.net/xwwwj/article/details/105372234一篇易懂的CAN通讯协议指南1一篇易懂的CAN通讯协议指南1-知乎(zhihu.com)视频推荐CAN总线个人知识总

深度学习部署:Windows安装pycocotools报错解决方法1.pycocotools库的简介2.pycocotools安装的坑3.解决办法更多Ai资讯:公主号AiCharm本系列是作者在跑一些深度学习实例时,遇到的各种各样的问题及解决办法,希望能够帮助到大家。ERROR:Commanderroredoutwithexitstatus1:'D:\Anaconda3\python.exe'-u-c'importsys,setuptools,tokenize;sys.argv[0]='"'"'C:\\Users\\46653\\AppData\\Local\\Temp\\pip-instal

我完全不是程序员,正在学习使用Ruby和Rails框架进行编程。我目前正在使用Ruby1.8.7和Rails3.0.3,但我想知道我是否应该升级到Ruby1.9,因为我真的没有任何升级的“遗留”成本。缺点是什么?我是否会遇到与普通gem的兼容性问题,或者甚至其他我不太了解甚至无法预料的问题? 最佳答案 你应该升级。不要坚持从1.8.7开始。如果您发现不支持1.9.2的gem,请避免使用它们(因为它们很可能不被维护)。如果您对gem是否兼容1.9.2有任何疑问,您可以在以下位置查看:http://www.railsplugins.or

如何学习ruby的正则表达式?(对于假人) 最佳答案 http://www.rubular.com/在Ruby中使用正则表达式时是一个很棒的工具,因为它可以立即将结果可视化。 关于ruby-我如何学习ruby的正则表达式?,我们在StackOverflow上找到一个类似的问题: https://stackoverflow.com/questions/1881231/

我想在Ruby的TCPServer中获取客户端的IP地址。以及(如果可能的话)MAC地址。例如,Ruby中的时间服务器,请参阅评论。tcpserver=TCPServer.new("",80)iftcpserverputs"Listening"loopdosocket=tcpserver.acceptifsocketThread.newdoputs"Connectedfrom"+#HERE!HowcanigettheIPAddressfromtheclient?socket.write(Time.now.to_s)socket.closeendendendend非常感谢!

深度学习12.CNN经典网络VGG16一、简介1.VGG来源2.VGG分类3.不同模型的参数数量4.3x3卷积核的好处5.关于学习率调度6.批归一化二、VGG16层分析1.层划分2.参数展开过程图解3.参数传递示例4.VGG16各层参数数量三、代码分析1.VGG16模型定义2.训练3.测试一、简介1.VGG来源VGG(VisualGeometryGroup)是一个视觉几何组在2014年提出的深度卷积神经网络架构。VGG在2014年ImageNet图像分类竞赛亚军,定位竞赛冠军;VGG网络采用连续的小卷积核(3x3)和池化层构建深度神经网络,网络深度可以达到16层或19层,其中VGG16和VGG

文章目录1、自相关函数ACF2、偏自相关函数PACF3、ARIMA(p,d,q)的阶数判断4、代码实现1、引入所需依赖2、数据读取与处理3、一阶差分与绘图4、ACF5、PACF1、自相关函数ACF自相关函数反映了同一序列在不同时序的取值之间的相关性。公式:ACF(k)=ρk=Cov(yt,yt−k)Var(yt)ACF(k)=\rho_{k}=\frac{Cov(y_{t},y_{t-k})}{Var(y_{t})}ACF(k)=ρk=Var(yt)Cov(yt,yt−k)其中分子用于求协方差矩阵,分母用于计算样本方差。求出的ACF值为[-1,1]。但对于一个平稳的AR模型,求出其滞

前面一篇关于智能合约翻译文讲到了,是一种计算机程序,既然是程序,那就可以使用程序语言去编写智能合约了。而若想玩区块链上的项目,大部分区块链项目都是开源的,能看得懂智能合约代码,或找出其中的漏洞,那么,学习Solidity这门高级的智能合约语言是有必要的,当然,这都得在公链``````以太坊上,毕竟国内的联盟链有些是不兼容Solidity。Solidity是一种面向对象的高级语言,用于实现智能合约。智能合约是管理以太坊状态下的账户行为的程序。Solidity是运行在以太坊(Ethereum)虚拟机(EVM)上,其语法受到了c++、python、javascript影响。Solidity是静态类型