锁存器(Latch),是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值。仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

当电平信号无效时,输出信号随输入信号变化,就像通过了缓冲器;当电平有效时,输出信号被锁存。激励信号的任何变化,都将直接引起锁存器输出状态的改变,很有可能会因为瞬态特性不稳定而产生振荡现象。

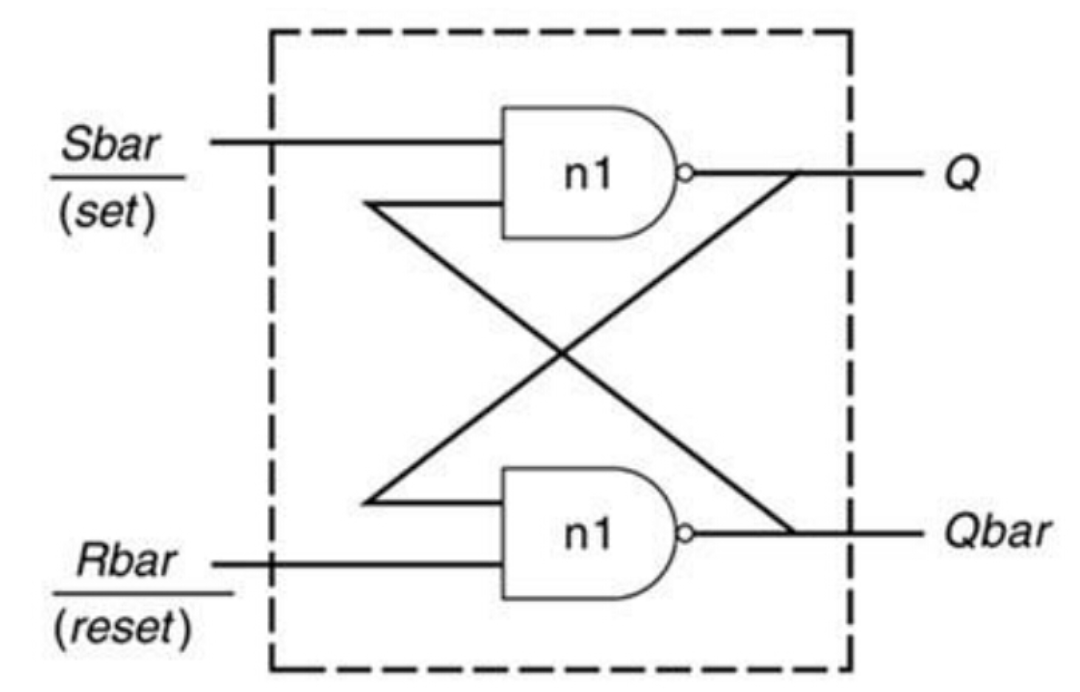

锁存器示意图如下:

触发器(flip-flop),是边沿敏感的存储单元,数据存储的动作(状态转换)由某一信号的上升沿或者下降沿进行同步的(限制存储单元状态转换在一个很短的时间内)。

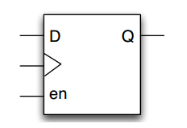

触发器示意图如下:

寄存器(register),在 Verilog 中用来暂时存放参与运算的数据和运算结果的变量。一个变量声明为寄存器时,它既可以被综合成触发器,也可能被综合成 Latch,甚至是 wire 型变量。但是大多数情况下我们希望它被综合成触发器,但是有时候由于代码书写问题,它会被综合成不期望的 Latch 结构。

Latch 的主要危害有:

Latch 多用于门控时钟(clock gating)的控制,一般设计时,我们应当避免 Latch 的产生。

组合逻辑中,不完整的 if - else 结构,会产生 latch。

例如下面的模型,if 语句中缺少 else 结构,系统默认 else 的分支下寄存器 q 的值保持不变,即具有存储数据的功能,所以寄存器 q 会被综合成 latch 结构。

module module1_latch1(

input data,

input en ,

output reg q) ;

always @(*) begin

if (en) q = data ;

end

endmodule

避免此类 latch 的方法主要有 2 种,一种是补全 if-else 结构,或者对信号赋初值。

例如,上面模型中的always语句,可以改为以下两种形式:

// 补全条件分支结构

always @(*) begin

if (en) q = data ;

else q = 1'b0 ;

end

//赋初值

always @(*) begin

q = 1'b0 ;

if (en) q = data ; //如果en有效,改写q的值,否则q会保持为0

end

但是在时序逻辑中,不完整的 if - else 结构,不会产生 latch,例如下面模型。

这是因为,q 寄存器具有存储功能,且其值在时钟的边沿下才会改变,这正是触发器的特性。

module module1_ff(

input clk ,

input data,

input en ,

output reg q) ;

always @(posedge clk) begin

if (en) q <= data ;

end

endmodule

在组合逻辑中,当条件语句中有很多条赋值语句时,每个分支条件下赋值语句的不完整也是会产生 latch。

其实对每个信号的逻辑拆分来看,这也相当于是 if-else 结构不完整,相关寄存器信号缺少在其他条件下的赋值行为。例如:

module module1_latch11(

input data1,

input data2,

input en ,

output reg q1 ,

output reg q2) ;

always @(*) begin

if (en) q1 = data1 ;

else q2 = data2 ;

end

endmodule

这种情况也可以通过补充完整赋值语句或赋初值来避免 latch。例如:

always @(*) begin

//q1 = 0; q2 = 0 ; //或在这里对 q1/q2 赋初值

if (en) begin

q1 = data1 ;

q2 = 1'b0 ;

end

else begin

q1 = 1'b0 ;

q2 = data2 ;

end

end

case 语句产生 Latch 的原理几乎和 if 语句一致。在组合逻辑中,当 case 选项列表不全且没有加 default 关键字,或有多个赋值语句不完整时,也会产生 Latch。例如:

module module1_latch2(

input data1,

input data2,

input [1:0] sel ,

output reg q ) ;

always @(*) begin

case(sel)

2'b00: q = data1 ;

2'b01: q = data2 ;

endcase

end

endmodule

当然,消除此种 latch 的方法也是 2 种,将 case 选项列表补充完整,或对信号赋初值。

补充完整 case 选项列表时,可以罗列所有的选项结果,也可以用 default 关键字来代替其他选项结果。

例如,上述 always 语句有以下 2 种修改方式。

always @(*) begin

case(sel)

2'b00: q = data1 ;

2'b01: q = data2 ;

default: q = 1'b0 ;

endcase

end

always @(*) begin

case(sel)

2'b00: q = data1 ;

2'b01: q = data2 ;

2'b10, 2'b11 :

q = 1'b0 ;

endcase

end

在组合逻辑中,如果一个信号的赋值源头有其信号本身,或者判断条件中有其信号本身的逻辑,则也会产生 latch。因为此时信号也需要具有存储功能,但是没有时钟驱动。此类问题在 if 语句、case 语句、问号表达式中都可能出现,例如:

//signal itself as a part of condition

reg a, b ;

always @(*) begin

if (a & b) a = 1'b1 ; //a -> latch

else a = 1'b0 ;

end

//signal itself are the assigment source

reg c;

wire [1:0] sel ;

always @(*) begin

case(sel)

2'b00: c = c ; //c -> latch

2'b01: c = 1'b1 ;

default: c = 1'b0 ;

endcase

end

//signal itself as a part of condition in "? expression"

wire d, sel2;

assign d = (sel2 && d) ? 1'b0 : 1'b1 ; //d -> latch

避免此类 Latch 的方法,就只有一种,即在组合逻辑中避免这种写法,信号不要给信号自己赋值,且不要用赋值信号本身参与判断条件逻辑。

例如,如果不要求立刻输出,可以将信号进行一个时钟周期的延时再进行相关逻辑的组合。上述第一个产生 Latch 的代码可以描述为:

reg a, b ;

reg a_r ;

always (@posedge clk)

a_r <= a ;

always @(*) begin

if (a_r & b) a = 1'b1 ; //there is no latch

else a = 1'b0 ;

end

如果组合逻辑中 always@() 块内敏感列表没有列全,该触发的时候没有触发,那么相关寄存器还是会保存之前的输出结果,因而会生成锁存器。

这种情况,把敏感信号补全或者直接用 always@(*) 即可消除 latch。

总之,为避免 latch 的产生,在组合逻辑中,需要注意以下几点:

我正在处理旧代码的一部分。beforedoallow_any_instance_of(SportRateManager).toreceive(:create).and_return(true)endRubocop错误如下:Avoidstubbingusing'allow_any_instance_of'我读到了RuboCop::RSpec:AnyInstance我试着像下面那样改变它。由此beforedoallow_any_instance_of(SportRateManager).toreceive(:create).and_return(true)end对此:let(:sport_

目录一、inout在设计文件中的使用方法1.1、inout的第一种使用方法1.2、inout实现的第二种使用方法1.3、inout使用总结 二、inout在仿真测试中的使用方法一、inout在设计文件中的使用方法在FPGA的设计过程中,有时候会遇到双向信号(既能作为输出,也能作为输入的信号叫双向信号)。比如,IIC总线中的SDA信号就是一个双向信号,QSPIFlash的四线操作的时候四根信号线均为双向信号。在Verilog中用关键字inout定义双向信号,这里总结一下双向信号的处理方法。1.1、inout的第一种使用方法 实际上,双向信号的本质是由一个三态门组成的,三态门可以输出高电平,低电

赋值时是否可以避免这种影响:irb(main):584:0>a=true=>trueirb(main):584:0>我有一个代码有很多赋值,当我试图测试它时,由于所有这些返回值,我看不到结果:truefalsetruefalsetruetrue.. 最佳答案 您可以启动irb或附加--noecho选项的控制台。$irb--noecho2.0.0p353:001>true2.0.0p353:002>否则,如果控制台由另一个进程启动,只需设置conf.echo=false$irb2.0.0p353:001>true=>true2.0.0

有没有一种方法可以避免hidden_field方法将View中的值传递给Controller?出于安全原因,我更喜欢Controller方法。不幸的是,strong_parameters不支持值对@variables。EDIT6/181:00PMESTI'verenamedmygaragescontrollertoappointmentscars_controllernolongercreatesanewappointment(formallygarages).Anewappointmentiscreatedintheappointments_controller我目前的结构路

我需要将目录中的一堆文件上传到S3。由于上传所需的90%以上的时间都花在了等待http请求完成上,所以我想以某种方式同时执行其中的几个。Fibers能帮我解决这个问题吗?它们被描述为解决此类问题的一种方法,但我想不出在http调用阻塞时我可以做任何工作的任何方法。有什么方法可以在没有线程的情况下解决这个问题? 最佳答案 我没有使用1.9中的纤程,但是1.8.6中的常规线程可以解决这个问题。尝试使用队列http://ruby-doc.org/stdlib/libdoc/thread/rdoc/classes/Queue.html查看文

我正在用Ruby编写类似curses的程序,我正在使用stty和ansi转义字符来实现我想要的。当我想获得用户输入时,我的问题就出现了。像许多基于控制台的程序一样,我想从终端底部获取用户输入。因此,我将光标放在屏幕底部并调用Readline.readline(或任何获取用户输入的方法)。像往常一样,它会读取所有内容,直到我按下回车键,并打印一个换行符。由于光标位于终端的最后一行,它会滚动一行,这会弄乱屏幕。我怎样才能避免这种情况?我试图使用stty来停止回显换行符,但我没有成功。也许可以使用stty来阻止终端滚动?当然,我可以编写自己的方法来通过一次读取一个字符(并捕获“返回”)来捕获

我有以下代码conn=Faraday.new(:url=>'http://www.mapquestapi.com')do|faraday|faraday.response:logger#logrequeststoSTDOUTfaraday.adapterFaraday.default_adapter#makerequestswithNet::HTTPfaraday.options.params_encoder=Faraday::FlatParamsEncoderendresponse=conn.getdo|req|req.url'/geocoding/v1/batch'req.para

这个问题在这里已经有了答案:RubyStyle:Howtocheckwhetheranestedhashelementexists(16个答案)HowtoavoidNoMethodErrorformissingelementsinnestedhashes,withoutrepeatednilchecks?(16个答案)关闭7年前。如果我尝试访问不存在的哈希元素,我会收到NoMethodError:undefinedmethod'[]'fornil:NilClass。但是,我无法预测会出现哪些元素。@param_info={}@param_info["drug"]["name"]#=>N

我正在打开非常大的YAML文件。这需要一段时间。但在打开它之后,它正在打印所有内容-并且它花费了很多倍的时间。那么如何避免在Ruby控制台中打印结果:data=YAML.load_file(...)#some1GBdatafile. 最佳答案 我假设您是在控制台中执行此操作。如果我不想看到输出,我通常只添加“;:ok”。data=YAML.load_file(...);:ok 关于ruby-在控制台执行命令后避免打印,我们在StackOverflow上找到一个类似的问题:

是否已就如何避免因可变状态导致的记忆化错误达成共识?在此示例中,缓存结果的状态发生了变化,因此在第二次调用时给出了错误的结果。classGreeterdefinitialize@greeting_cache={}enddefexpensive_greeting_calculation(formality)caseformalitywhen:casualthen"Hi"when:formalthen"Hello"endenddefgreeting(formality)unless@greeting_cache.has_key?(formality)@greeting_cache[form