目录

AXI简介

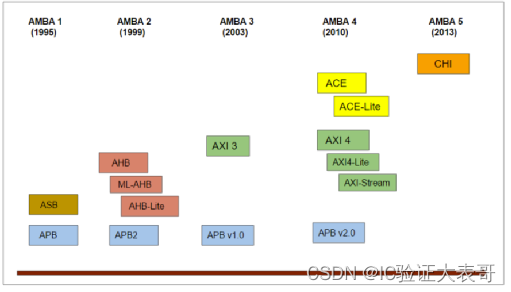

在介绍AXI协议前,先看下AMBA的演进情况。

随着移动和智能手机时代发生了进一步的演进,SOC集成了2/4/8核处理器和共享cache,并且需要跨内存子系统的硬件管理一致性。这导致了在AMBA修订版4中引入了ACE(AXI一致性协议扩展)。

在当前HPC和数据中心市场的异构计算时代,单个芯片上集成越来越多的处理器核心以及GPU、DSP、FPGA、内存控制器和IO子系统。2013年,AMBA5引入了CHI协议,作为AXI/ACE协议的重新设计。基于信号的AXI/ACE协议被新的基于包的CHI协议所取代。

1、APB:高级外围设备总线(APB)用于连接低带宽的外围设备。它是一个简单的非流水线协议。读写操作共享同一组信号,不支持burst数据传输。最新的规范(APB2.0)可以在ARM网站上找到,是最容易学习的AMBA 协议。

2、AHB:高级高性能总线(AHB)用于连接共享总线上需要更高带宽的组件。这些slave组件可以是内部内存或外部内存接口、DMA、DSP等。AHB可以通过burst数据传输来获得更高的带宽。

3、AHB-lite协议是AHB的一个简化版本。简化后只支持一个主设计,这消除了对任何仲裁、重试、分割事务等的需求。

4、高级可扩展接口(AXI)适合于高带宽和低延迟互连。这是一个点对点的互连,并克服了AHB、APB等共享总线协议在可连接的代理数量方面的限制性。该协议支持多个outstanding的数据传输、burst数据传输、单独的读写通道和支持不同的总线宽度。

5、AXI-lite协议是AXI的简化版本,简化后不支持突发数据传输。

6、AXI-stream协议是AXI协议的另一种风格,它只支持数据流从master 流到slave。与完整的AXI或AXI-lite不同,AXI-stream 协议中没有单独的读/写通道,因为其目的是只在一个方向上流。

7、ACE-AXI协议是AXI4协议的扩展,应用于在一个芯片上集成多个CPU核心与一致性cache的场景。ACE协议扩展了AXI读写数据通道,同时引入了单独的snoop 地址、snoop 数据和snoop 响应通道。这些额外的通道提供了实现基于snoop 的一致性协议的机制。

8、ACE-Lite—对于没有自己cache的agents ,但仍属于可共享一致性域的一部分,如DMA或网络接口agent,使用ACE-lite协议实现这种“单向”一致性。

9、CHI—ACE协议作为AXI的扩展而开发,以支持一致性互连。ACE协议使用了master/slave之间的信号电平通信,因此互连需要大量的线和增加的通道来进行snoops 和响应。这对于具有2/4核移动SOC 的小一致性clusters非常有效。随着SOC上集成越来越多的一致性clusters ——AMBA5修订版引入了CHI协议。CHI协议使用基于分层分组的通信协议,具有协议、链路层和物理层实现,还支持基于QoS的流控制和重试机制。

AXI 表示 Advanced eXtensible Interface(高级可扩展接口),它是由 Arm 定义的接口协议,包含在“高级微控制器总线架构 AMBA”标准中。

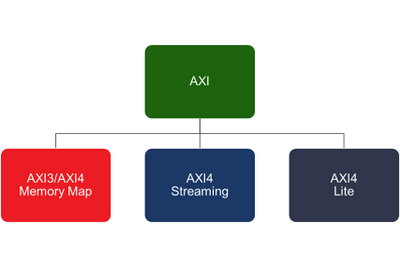

AXI4 接口 (AMBA 4.0) 分 3 种类型:

注 1 :本文不涵盖 AXI4-Stream 相关内容。此处“AXI”表示 AXI3、AXI4 和 AXI4-Lite。

注 2:AXI3 接口与 Full AXI 接口接近。

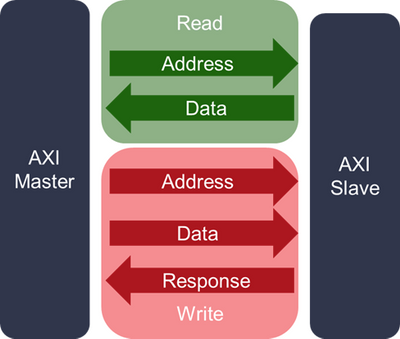

AXI 协议定义了 5 条通道:

通道 (channel) 是与 VALID 和 READY 信号关联的 AXI 信号的独立集合。

注:AXI4/AXI3/AXI4-Lite 接口只能用于读取(仅包含 2 条读取通道)或者只能用于写入(仅包含 3 条写入通道)。

任一通道上发射的每一条数据都称为一次传输 (transfer)。当 VALID 和 READY 信号均处于高位并且时钟存在上升沿时,就会发生传输。例如,在下图中,在 T3 处正在发生传输:

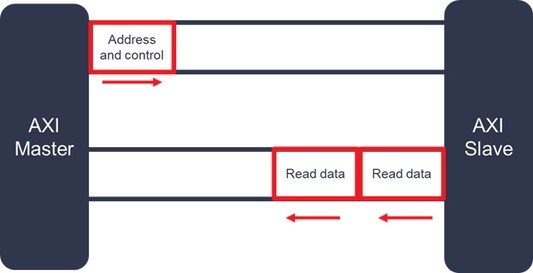

AXI 读传输事务需要在 2 条读取通道上发生多次传输。

请注意,根据下图所示,每个地址中可发生多次数据传输。此类型的传输事务称为突发 (burst)。

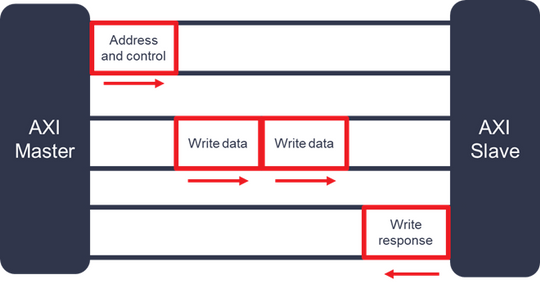

AXI 写入传输事务需要在 3 条读取通道上存在多次传输。

写响应通道 (Write Response Channel) 上可能的响应值包括:

注:读取传输事务同样包含响应值,但此响应通过读响应通道 (Read Response Channel) 来发射

突发传输。连续传输

是的,在配合每次传输的byte数,就可以确定下一个传输的地址。

因为AXI4协议规定主机上寄存器块的最小分块单元为4K Byte,每个从机的开始映射地址都是4KB的边界。这也影响了AXI4的一个读写规则,那就是一个burst传输不能跨越4KB的界限,否则就会引入将数据错误写入其他从机的风险。注意这个4KB的界限指的是MASTER的地址界限,例如一个burst中不能越过0xXXXX_X000的地址位。FFF=4095,

就是1024个寄存器,*4byte =4KB。

非对其传输指当传输的目标地址(byte)与寄存器的边界(word对齐)未对齐时,可以使用非对齐传输,例如一个传输在0x3地址开始,而不是0x0或者0x4,非对其传输只会影响一个burst传输中的第一笔数据,可采用WSTRB信号来表示第一个data中的哪几个byte是有效的,其余的数据还是正常的burst传输。

valid(表示地址/数据/应答输出有效信号)驱动到低电平

①主机ARVALID,AWVALID,WVALID为低电平;

② 从机接口必须驱动RVALID,BVALID为低电平;

③ 所有其他信号可以被驱动到任意值。

在复位后,主机可以在时钟上升沿驱动ARVALID,AWVALID,WVALID为高电平

• 读取地址,其信号名称以AR 开头。

• 读取信号名称以 R 开头的数据。

• 写入地址,信号名称以AW 开头。

• 写入信号名称以 W 开头的数据。

• 写入响应,其信号名称以 B 开头。

1、AXI3只支持多达16拍的burst 。而AXI4支持高达256拍的burst 。

2、AXI3支持write interleave。AXI4不支持write interleave(去掉了wid)

3、AXI3支持locked 传输,AXI4不支持locked 传输

4、AXI4支持QoS,AXI3不支持QoS。

为什么没有单独的read 响应通道?

VALID/READY握手机制只允许一个方向的数据流,所以对于读事务,数据(data和resp)从slave流向master,而对于写事务,数据从master流向slave,所以就需要单独的响应通道

为什么在burst 写中,不是每拍都有写响应。但是在burst 读中,每拍都有一个单独的读响应?

所有的AXI信道只在1个方向传递信息 ,所以才需要一个单独的写响应通道。在大多数应用中不管slave能不能接受完整的数据这个burst传输都会执行完成,slave无需在每一拍都返回ERROR响应

如何终止burst 传输?

不能。AXI不能够提前终止burst传输。对于写事务,master可以完成burst 传输,通过WSTRB信号丢弃掉无效数据即可,对于读事务同样也可以将读回的数据丢弃。

master 可以在burst 传输中间给WLAST吗?

不行。只有在burst 传输的最后一拍才能拉高WLAST,在burst传输的中间拉高WLAST是违反协议的行为。此外,许多slave设计不会使用WLAST信号,而是自己计数,所以master拉高WLAST也不会提前终止burst传输。

Slave能在burst传输完成之前置起rlast么?

和上题一样,slave在burst传输的未完成就拉起RLAST是违反协议的行为。master同样也有可能不依赖RLAST

既然WLAST和RLAST可能不被使用,那为什么需要支持这两个信号?

为了支持所有的master和slave,无论其是否依赖这两个信号传输数据。

Exclusive 读写事务是什么?在哪里使用?

如果一个内存区域被多个master共享,某个master需要希望确保在没有其他master更改共享内存的情况下完成读然后写的序列,就可以使用Exclusive 传输

读取事务是否有可能在一个周期内完成?

需要至少1个时钟周期传递地址(从master到slave),然后至少1个时钟周期传递数据(从slave到master)。

axi slave是如何支持Exclusive 访问的?

假设 AXI Master1(M1)已经启动了对地址位置12h100到12h10F的exclusive 读写。那么相应的salve将开始监视由M1给出的这些地址。如果此时该地址被其他master执行写操作,此时会返回Exclusive error

发送给slave的读写地址和读写数据是如何关联的?

AR总线和AW总线是独立的,不管读写请求的地址是否顺序发出的,响应的数据都可能是无序的,他们之间是通过awid和arid对应配对的(axi3)axi4去掉了wid,所以写通道的写顺序必须与写地址通道保持一致

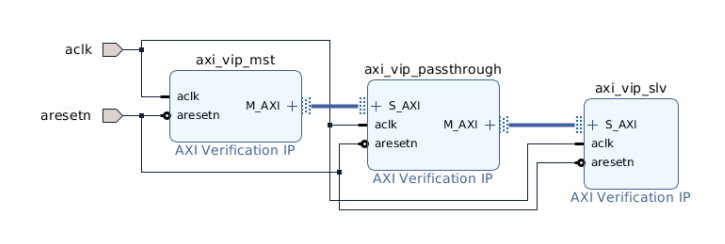

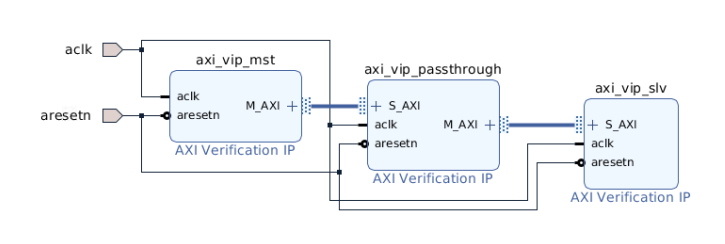

AXI Verification IP (AXI VIP) 对 AXI4 接口进行仿真。

AXI Verification IP (AXI VIP) 是支持用户对 AXI4 和 AXI4-Lite 进行仿真的 IP。它还可作为 AXI Protocol Checker 来使用。

此 IP 只是仿真 IP,将不进行综合,它将在直通 (Pass-through) 配置中被连线所替代。

AXI VIP IP 核用途如下:

它支持 5 种不同配置:

AXI VIP 的设计示例包含 3 个 AXI VIP:其中一个配置为 Master、一个配置为 Pass-through,另一个配置为 Slave。

工程中包含了多个测试激励文件 (Test Bench) 源文件,以匹配不同 AXI VIP 组合。

注:所有测试激励文件都是以 SystemVerilog 语言编写的。要使用 AXI VIP 的全部功能,应将此 IP 例化包含在 SystemVerilog 测试激励文件中。

Snop AXI VIP overriew (TBC)

AXI VIP 的设计示例包含 3 个 AXI VIP:其中一个配置为 Master、一个配置为 Pass-through,另一个配置为 Slave。

注:所有测试激励文件都是以 SystemVerilog 语言编写的。要使用 AXI VIP 的全部功能,应将此 IP 例化包含在 SystemVerilog 测试激励文件中。

关闭。这个问题是opinion-based.它目前不接受答案。想要改进这个问题?更新问题,以便editingthispost可以用事实和引用来回答它.关闭4年前。Improvethisquestion我想在固定时间创建一系列低音和高音调的哔哔声。例如:在150毫秒时发出高音调的蜂鸣声在151毫秒时发出低音调的蜂鸣声200毫秒时发出低音调的蜂鸣声250毫秒的高音调蜂鸣声有没有办法在Ruby或Python中做到这一点?我真的不在乎输出编码是什么(.wav、.mp3、.ogg等等),但我确实想创建一个输出文件。

这里是Ruby新手。完成一些练习后碰壁了。练习:计算一系列成绩的字母等级创建一个方法get_grade来接受测试分数数组。数组中的每个分数应介于0和100之间,其中100是最大分数。计算平均分并将字母等级作为字符串返回,即“A”、“B”、“C”、“D”、“E”或“F”。我一直返回错误:avg.rb:1:syntaxerror,unexpectedtLBRACK,expecting')'defget_grade([100,90,80])^avg.rb:1:syntaxerror,unexpected')',expecting$end这是我目前所拥有的。我想坚持使用下面的方法或.join,

在应用开发中,有时候我们需要获取系统的设备信息,用于数据上报和行为分析。那在鸿蒙系统中,我们应该怎么去获取设备的系统信息呢,比如说获取手机的系统版本号、手机的制造商、手机型号等数据。1、获取方式这里分为两种情况,一种是设备信息的获取,一种是系统信息的获取。1.1、获取设备信息获取设备信息,鸿蒙的SDK包为我们提供了DeviceInfo类,通过该类的一些静态方法,可以获取设备信息,DeviceInfo类的包路径为:ohos.system.DeviceInfo.具体的方法如下:ModifierandTypeMethodDescriptionstatic StringgetAbiList()Obt

基础版云数据库RDS的产品系列包括基础版、高可用版、集群版、三节点企业版,本文介绍基础版实例的相关信息。RDS基础版实例也称为单机版实例,只有单个数据库节点,计算与存储分离,性价比超高。说明RDS基础版实例只有一个数据库节点,没有备节点作为热备份,因此当该节点意外宕机或者执行重启实例、变更配置、版本升级等任务时,会出现较长时间的不可用。如果业务对数据库的可用性要求较高,不建议使用基础版实例,可选择其他系列(如高可用版),部分基础版实例也支持升级为高可用版。基础版与高可用版的对比拓扑图如下所示。优势 性能由于不提供备节点,主节点不会因为实时的数据库复制而产生额外的性能开销,因此基础版的性能相对于

我使用irb。下面是我写的代码。“斧头”..“bc”我期待"ax""ay""az""ba"bb""bc"但结果只是“斧头”..“bc”我该如何纠正?谢谢。 最佳答案 >puts("ax".."bc").to_aaxayazbabbbc 关于ruby-从结束值创建一系列字符串,我们在StackOverflow上找到一个类似的问题: https://stackoverflow.com/questions/7617092/

使用RubyonRails,我使用给定的增量(例如每30分钟)用时间填充“选择”。目前我正在YAML文件中写出所有的可能性,但我觉得有一种更巧妙的方法。我想我想提供一个开始时间、一个结束时间、一个增量,并且目前只提供一个名为“关闭”的选项(想想“business_hours”)。所以,我的选择可能会显示:'Closed'5:00am5:30am6:00am...[allthewayto]...11:30pm谁能想出更好的方法,或者只是将它们全部“拼写”出来的最佳方法? 最佳答案 此答案基于@emh的答案。defcreate_hour

有道无术,术尚可求,有术无道,止于术。本系列SpringBoot版本3.0.4本系列SpringSecurity版本6.0.2本系列SpringAuthorizationServer版本1.0.2源码地址:https://gitee.com/pearl-organization/study-spring-security-demo文章目录前言1.OAuth2AuthorizationServerMetadataEndpointFilter2.OAuth2AuthorizationEndpointFilter3.OidcProviderConfigurationEndpointFilter4.N

我使用geokit和geokit-railsgemforrails有一段时间了,但我还没有找到答案的一个问题是如何找到一组点的计算聚合中心。我知道如何计算两点之间的距离,但不会超过2。我的理由是,我在同一个城市中有一系列的点……一切都完美的城市会有一个我可以使用的中心,但有些城市,比如柏林没有一个完美的中心。他们有多个中心,我只想使用我数据库中的所有地点列表来计算特定分布的中心。还有其他人遇到过这个问题吗?有什么建议吗?谢谢 最佳答案 之前从未使用过Geokit,这个操作背后的数学原理相对容易自己实现。假设这些点由纬度和经度组成,您

我有一个名为“FizzBuzz”的游戏的非常简单的Ruby实现(即给定输入数字,如果数字是3的倍数,则返回“Fizz”,如果是5的倍数,则返回“Buzz”,如果是多个,则返回“FizzBuzz”如果它不符合任何先前的条件,则两者和原始数字):classFizzBuzzdefanswer(number)multiple3=number%3==0multiple5=number%5==0returncasewhen(multiple3andmultiple5)then"FizzBuzz"whenmultiple3then"Fizz"whenmultiple5then"Buzz"el

一、概述在之前的一篇博文中,记录了AT24C01、AT24C02芯片的读写驱动,先将之前的相关文章include一下:1.IIC驱动:4位数码管显示模块TM1637芯片C语言驱动程序2.AT24C01/AT24C02读写:AT24C01/AT24C02系列EEPROM芯片单片机读写驱动程序本文记录分享AT24C04、AT24C08、AT24C16芯片的单片机C语言读写驱动程序。二、芯片对比介绍型号容量bit容量byte页数字节/页器件寻址位可寻址器件数WordAddress位数/字节数备注AT24C044k5123216A2A149/1WordAddress使用P0位AT24C088k1024