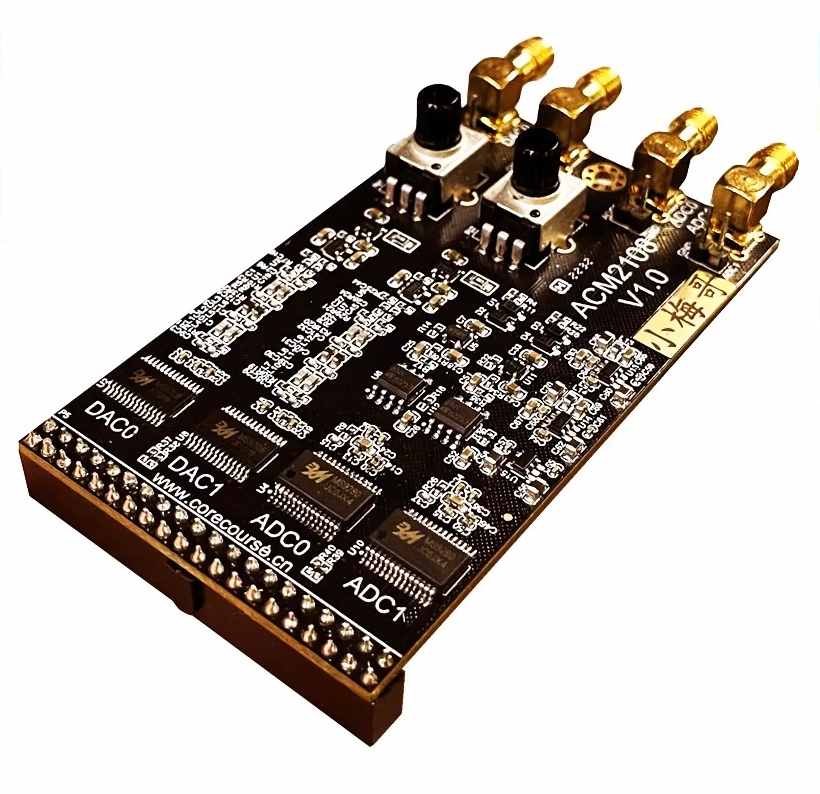

这次设计一个DDS信号发生器。该设计的特点有:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company: GDUT

// Engineer: Lclone

//

// Create Date: 2023/02/02 22:34:21

// Design Name: DDS_ACM2108

// Module Name: DDS_ACM2108

// Project Name: DDS_ACM2108

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module DDS_ACM2108(

input Clk,

input Rst_n,

output DA_Clk_ch1,

output [7:0] DA_data_ch1,

output DA_Clk_ch2,

output [7:0] DA_data_ch2,

output AD_Clk_ch1,

input [7:0] AD_data_ch1,

output AD_Clk_ch2,

input [7:0] AD_data_ch2

);

wire Clk_125M;

wire [31:0] Fword_ch1;

wire [11:0] Pword_ch1;

wire [ 1:0] mode_sel_ch1;

wire [31:0] Fword_ch2;

wire [11:0] Pword_ch2;

wire [ 1:0] mode_sel_ch2;

reg [7:0] AD_data_ch1_reg;

reg [7:0] AD_data_ch2_reg;

wire Wave_rst_p;

always@(posedge Clk)begin

AD_data_ch1_reg <= AD_data_ch1;

AD_data_ch2_reg <= AD_data_ch2;

end

ila_0 ila_0_DA (

.clk(Clk_125M), // input wire clk

.probe0(DA_data_ch1), // input wire [7:0] probe0

.probe1(DA_data_ch2) // input wire [7:0] probe1

);

ila_1 ila_1_AD_ch1 (

.clk(Clk), // input wire clk

.probe0(AD_data_ch1) // input wire [7:0] probe0

);

ila_1 ila_1_AD_ch2 (

.clk(Clk), // input wire clk

.probe0(AD_data_ch2) // input wire [7:0] probe0

);

clk_wiz_0 clk_wiz_0_inst (

// Clock out ports

.clk_out1(Clk_125M), // output clk_out1

// Clock in ports

.clk_in1(Clk)); // input clk_in1

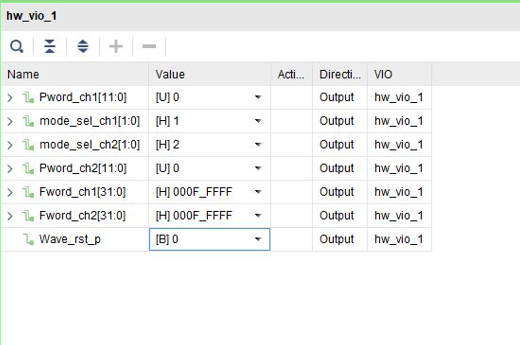

DDS_Cmd_VIO DDS_Cmd_VIO_inst (

.clk(Clk_125M), // input wire clk

.probe_out0(Fword_ch1), // output wire [31 : 0] probe_out0

.probe_out1(Pword_ch1), // output wire [11 : 0] probe_out1

.probe_out2(mode_sel_ch1), // output wire [1 : 0] probe_out2

.probe_out3(Fword_ch2), // output wire [31 : 0] probe_out3

.probe_out4(Pword_ch2), // output wire [11 : 0] probe_out4

.probe_out5(mode_sel_ch2), // output wire [1 : 0] probe_out5

.probe_out6(Wave_rst_p) // output wire [1 : 0] probe_out5

);

DDS_Base DDS_Base_ch1(

.Clk (Clk_125M),

.Rst_n (Rst_n & ~Wave_rst_p),

.Fword (Fword_ch1),

.Pword (Pword_ch1),

.mode_sel (mode_sel_ch1),

.DA_Clk (DA_Clk_ch1),

.Signal_data (DA_data_ch1)

);

DDS_Base DDS_Base_ch2(

.Clk (Clk_125M),

.Rst_n (Rst_n & ~Wave_rst_p),

.Fword (Fword_ch2),

.Pword (Pword_ch2),

.mode_sel (mode_sel_ch2),

.DA_Clk (DA_Clk_ch2),

.Signal_data (DA_data_ch2)

);

assign AD_Clk_ch1 = Clk;

assign AD_Clk_ch2 = Clk;

endmodule

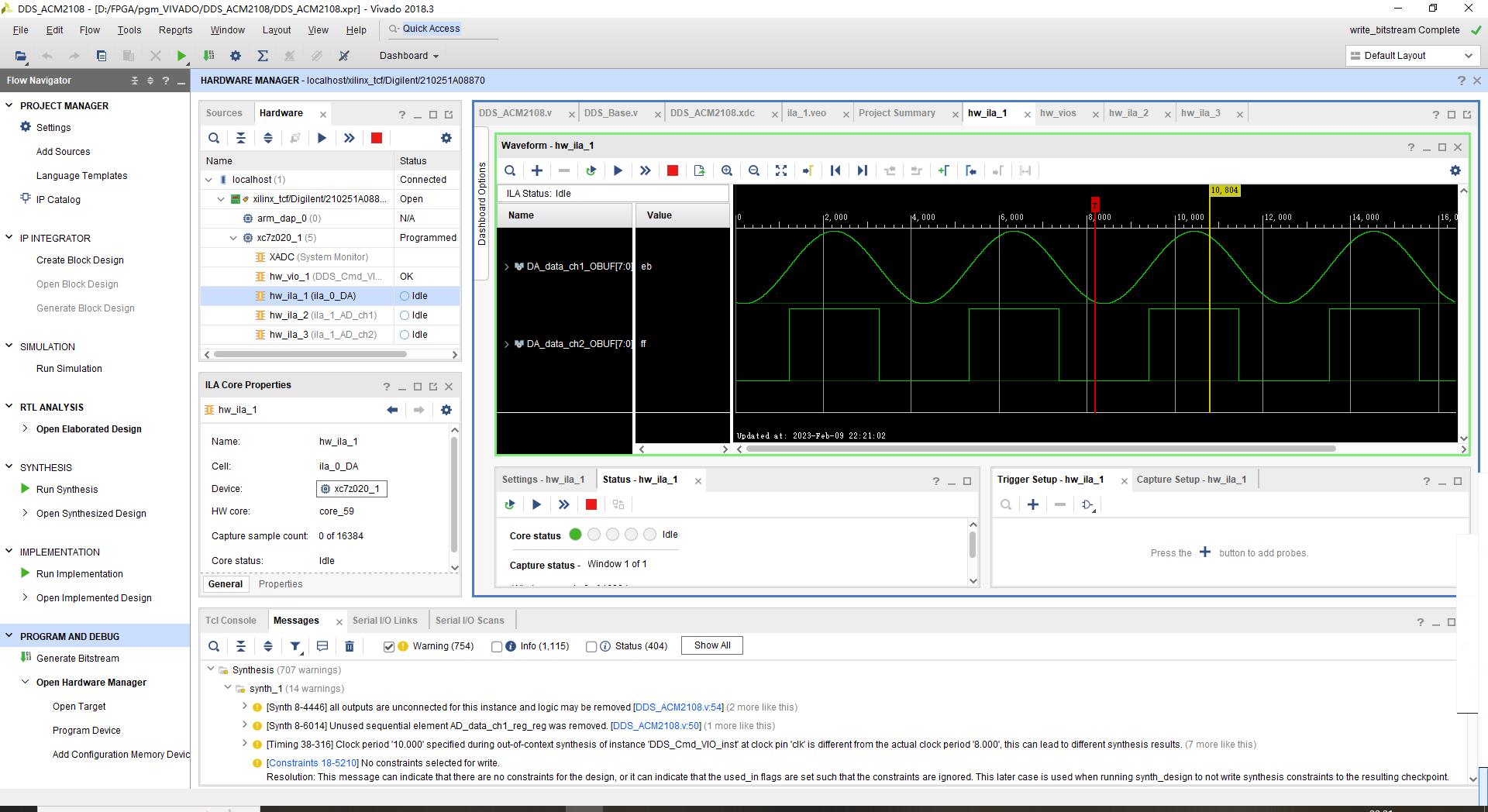

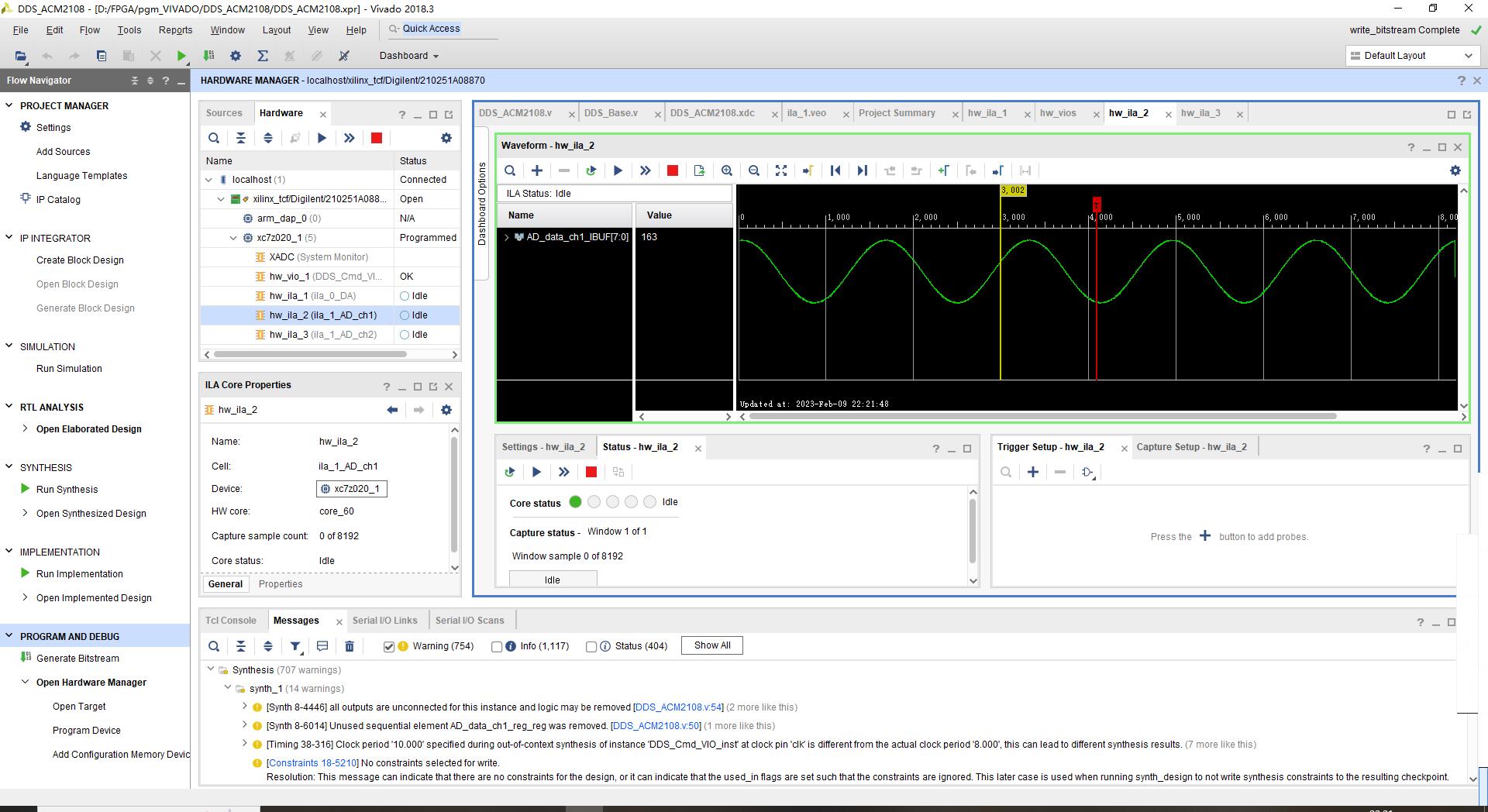

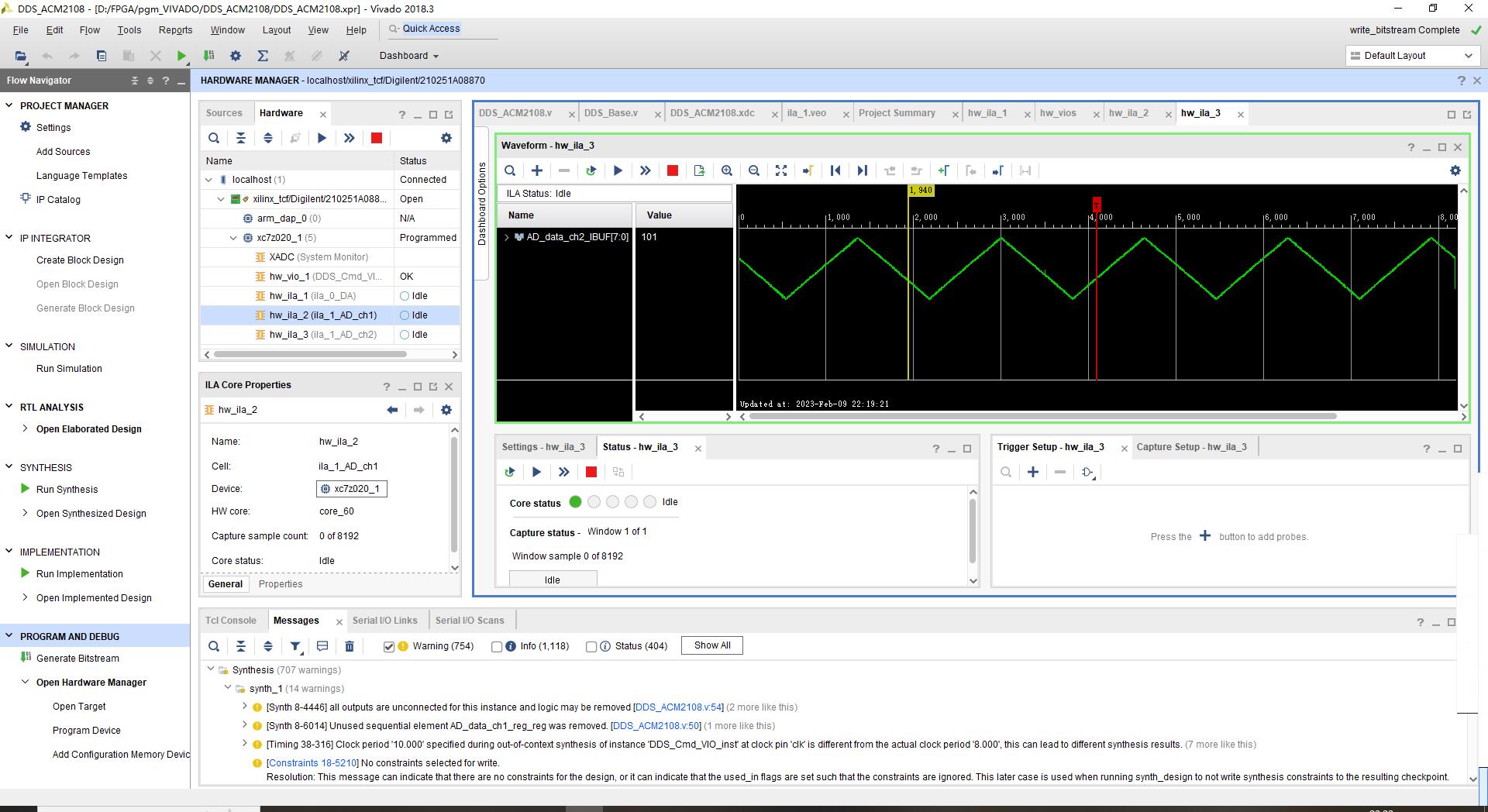

我将ACM2108的ad接口与da接口进行连接,然后通过ila观察AD和DA的波形来观察设计是否成功。

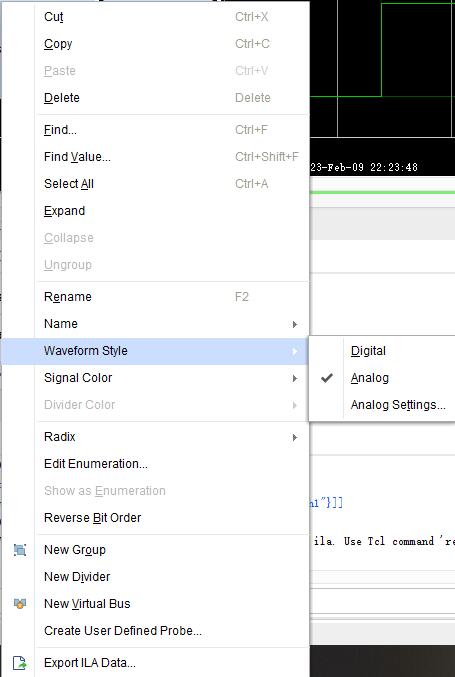

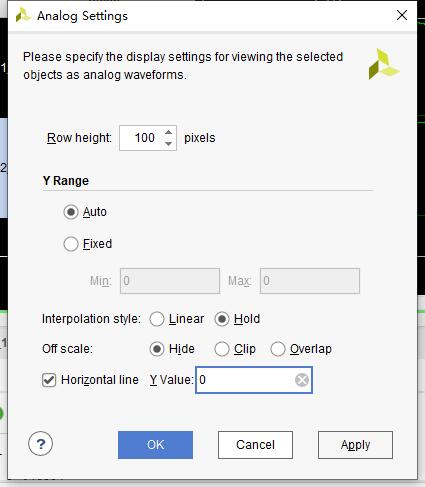

在观察方波信号的时候,vivado可能会帮我们的波形做处理,导致我们观察的方波变成三角波,这里我们在Analog Settings里将Interpolation style改为Hold即可设置为正常显示的波形。

以下是上板后的结果:

程序上板后,可以输出频率和相位可调的正弦波、方波、三角波。

我有一个模型:classItem项目有一个属性“商店”基于存储的值,我希望Item对象对特定方法具有不同的行为。Rails中是否有针对此的通用设计模式?如果方法中没有大的if-else语句,这是如何干净利落地完成的? 最佳答案 通常通过Single-TableInheritance. 关于ruby-on-rails-Rails-子类化模型的设计模式是什么?,我们在StackOverflow上找到一个类似的问题: https://stackoverflow.co

我将应用程序升级到Rails4,一切正常。我可以登录并转到我的编辑页面。也更新了观点。使用标准View时,用户会更新。但是当我添加例如字段:name时,它不会在表单中更新。使用devise3.1.1和gem'protected_attributes'我需要在设备或数据库上运行某种更新命令吗?我也搜索过这个地方,找到了许多不同的解决方案,但没有一个会更新我的用户字段。我没有添加任何自定义字段。 最佳答案 如果您想允许额外的参数,您可以在ApplicationController中使用beforefilter,因为Rails4将参数

导读:随着叮咚买菜业务的发展,不同的业务场景对数据分析提出了不同的需求,他们希望引入一款实时OLAP数据库,构建一个灵活的多维实时查询和分析的平台,统一数据的接入和查询方案,解决各业务线对数据高效实时查询和精细化运营的需求。经过调研选型,最终引入ApacheDoris作为最终的OLAP分析引擎,Doris作为核心的OLAP引擎支持复杂地分析操作、提供多维的数据视图,在叮咚买菜数十个业务场景中广泛应用。作者|叮咚买菜资深数据工程师韩青叮咚买菜创立于2017年5月,是一家专注美好食物的创业公司。叮咚买菜专注吃的事业,为满足更多人“想吃什么”而努力,通过美好食材的供应、美好滋味的开发以及美食品牌的孵

C#实现简易绘图工具一.引言实验目的:通过制作窗体应用程序(C#画图软件),熟悉基本的窗体设计过程以及控件设计,事件处理等,熟悉使用C#的winform窗体进行绘图的基本步骤,对于面向对象编程有更加深刻的体会.Tutorial任务设计一个具有基本功能的画图软件**·包括简单的新建文件,保存,重新绘图等功能**·实现一些基本图形的绘制,包括铅笔和基本形状等,学习橡皮工具的创建**·设计一个合理舒适的UI界面**注明:你可能需要先了解一些关于winform窗体应用程序绘图的基本知识,以及关于GDI+类和结构的知识二.实验环境Windows系统下的visualstudio2017C#窗体应用程序三.

目录前言滤波电路科普主要分类实际情况单位的概念常用评价参数函数型滤波器简单分析滤波电路构成低通滤波器RC低通滤波器RL低通滤波器高通滤波器RC高通滤波器RL高通滤波器部分摘自《LC滤波器设计与制作》,侵权删。前言最近需要学习放大电路和滤波电路,但是由于只在之前做音乐频谱分析仪的时候简单了解过一点点运放,所以也是相当从零开始学习了。滤波电路科普主要分类滤波器:主要是从不同频率的成分中提取出特定频率的信号。有源滤波器:由RC元件与运算放大器组成的滤波器。可滤除某一次或多次谐波,最普通易于采用的无源滤波器结构是将电感与电容串联,可对主要次谐波(3、5、7)构成低阻抗旁路。无源滤波器:无源滤波器,又称

项目介绍随着我国经济迅速发展,人们对手机的需求越来越大,各种手机软件也都在被广泛应用,但是对于手机进行数据信息管理,对于手机的各种软件也是备受用户的喜爱小学生兴趣延时班预约小程序的设计与开发被用户普遍使用,为方便用户能够可以随时进行小学生兴趣延时班预约小程序的设计与开发的数据信息管理,特开发了小程序的设计与开发的管理系统。小学生兴趣延时班预约小程序的设计与开发的开发利用现有的成熟技术参考,以源代码为模板,分析功能调整与小学生兴趣延时班预约小程序的设计与开发的实际需求相结合,讨论了小学生兴趣延时班预约小程序的设计与开发的使用。开发环境开发说明:前端使用微信微信小程序开发工具:后端使用ssm:VU

需求:要创建虚拟机,就需要给他提供一个虚拟的磁盘,我们就在/opt目录下创建一个10G大小的raw格式的虚拟磁盘CentOS-7-x86_64.raw命令格式:qemu-imgcreate-f磁盘格式磁盘名称磁盘大小qemu-imgcreate-f磁盘格式-o?1.创建磁盘qemu-imgcreate-fraw/opt/CentOS-7-x86_64.raw10G执行效果#ls/opt/CentOS-7-x86_64.raw2.安装虚拟机使用virt-install命令,基于我们提供的系统镜像和虚拟磁盘来创建一个虚拟机,另外在创建虚拟机之前,提前打开vnc客户端,在创建虚拟机的时候,通过vnc

我在我的项目中有一个用户和一个管理员角色。我使用Devise创建了身份验证。在我的管理员角色中,我没有任何确认。在我的用户模型中,我有以下内容:devise:database_authenticatable,:confirmable,:recoverable,:rememberable,:trackable,:validatable,:timeoutable,:registerable#Setupaccessible(orprotected)attributesforyourmodelattr_accessible:email,:username,:prename,:surname,:

我正在尝试创建密码规则来设计可恢复的密码更改。我通过passwords_controller.rb做了一个父类(superclass),但我需要在应用规则之前检查用户角色,但我所拥有的只是reset_password_token。 最佳答案 假设您的模型是用户:User.with_reset_password_token(your_token_here)Source 关于ruby-on-rails-设计通过reset_password_token获取用户,我们在StackOverflow

我已经使用Apartment设置了一个Rails5应用程序(1.2.0)和Devise(4.2.0)。由于某些DDNS问题,应用只能在app.myapp.com下访问(请注意子域app)。myapp.com重定向到app.myapp.com。我的用例是每个注册该应用的用户(租户)都应该通过他们的子域(例如tenant.myapp.com)访问他们的特定数据。用户不应限定在其子域内。基本上应该可以从任何子域登录。重定向到租户的正确子域由ApplicationController处理。根据Devise标准,登录页面位于app.myapp.com/users/sign_in。这就是问题开始的